75

TMS320C6748

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Submit Documentation Feedback

Product Folder Links: TMS320C6748

SpecificationsCopyright © 2009–2017, Texas Instruments Incorporated

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to VSS, USB0_VSSA33, USB0_VSSA, PLL0_VSSA, OSCVSS, RTC_VSS

(3) Up to a maximum of 24 hours.

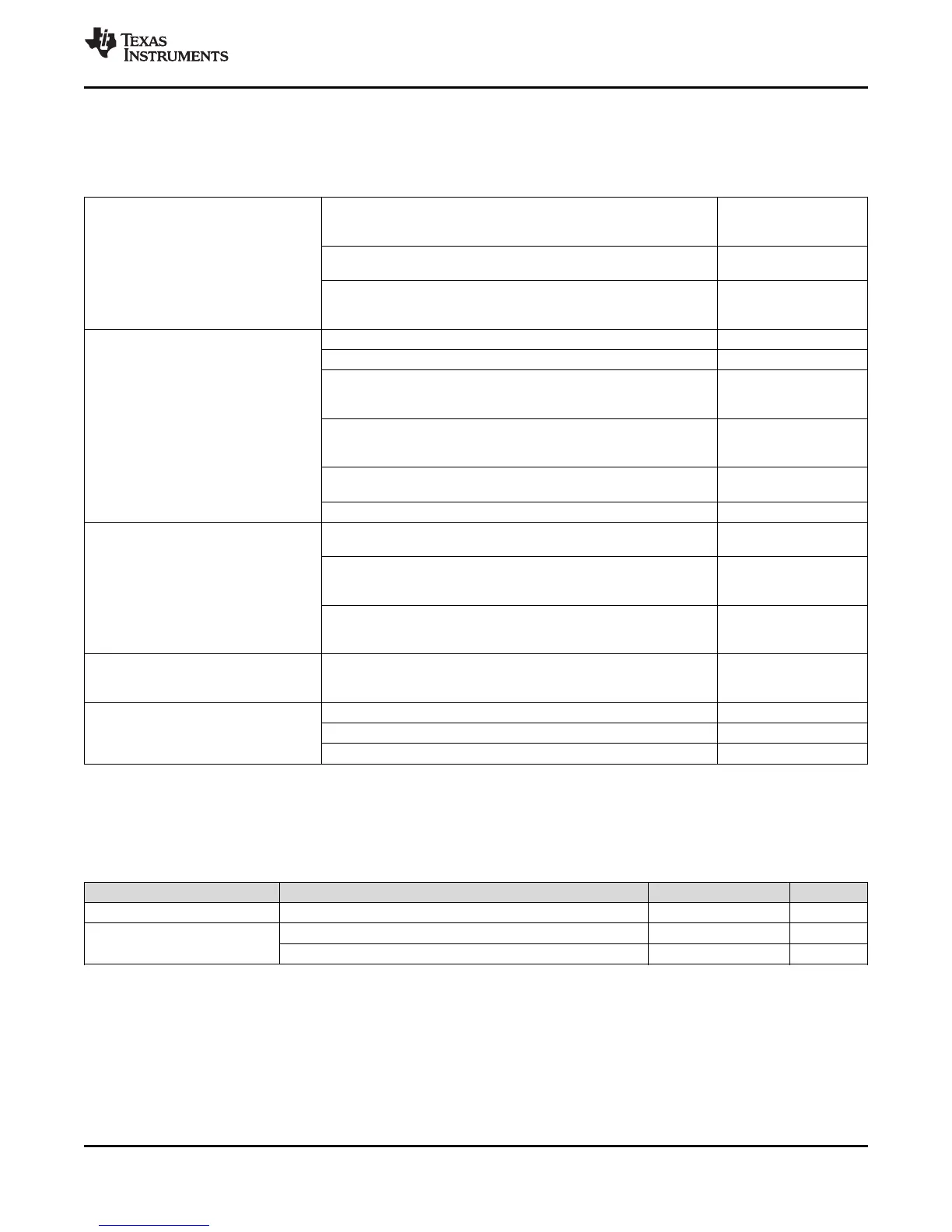

5 Specifications

5.1 Absolute Maximum Ratings Over Operating Junction Temperature Range

(Unless Otherwise Noted)

(1)

Supply voltage ranges

Core Logic, Variable and Fixed

(CVDD, RVDD, RTC_CVDD, PLL0_VDDA , PLL1_VDDA ,

SATA_VDD, USB_CVDD)

(2)

-0.5 V to 1.4 V

I/O, 1.8V

(USB0_VDDA18, USB1_VDDA18, SATA_VDDR, DDR_DVDD18)

(2)

-0.5 V to 2 V

I/O, 3.3V

(DVDD3318_A, DVDD3318_B, DVDD3318_C, USB0_VDDA33,

USB1_VDDA33)

(2)

-0.5 V to 3.8V

Input voltage (V

I

) ranges

Oscillator inputs (OSCIN, RTC_XI), 1.2V -0.3 V to CVDD + 0.3V

Dual-voltage LVCMOS inputs, 3.3V or 1.8V (Steady State) -0.3V to DVDD + 0.3V

Dual-voltage LVCMOS inputs, operated at 3.3V

(Transient Overshoot/Undershoot)

DVDD + 20%

up to 20% of Signal

Period

Dual-voltage LVCMOS inputs, operated at 1.8V

(Transient Overshoot/Undershoot)

DVDD + 30%

up to 30% of Signal

Period

USB 5V Tolerant IOs:

(USB0_DM, USB0_DP, USB0_ID, USB1_DM, USB1_DP)

5.25V

(3)

USB0 VBUS Pin 5.50V

(3)

Output voltage (V

O

) ranges

Dual-voltage LVCMOS outputs, 3.3V or 1.8V

(Steady State)

-0.3 V to DVDD + 0.3V

Dual-voltage LVCMOS outputs, operated at 3.3V

(Transient Overshoot/Undershoot)

DVDD + 20%

up to 20% of Signal

Period

Dual-voltage LVCMOS outputs, operated at 1.8V

(Transient Overshoot/Undershoot)

DVDD + 30%

up to 30% of Signal

Period

Clamp Current

Input or Output Voltages 0.3V above or below their respective power

rails. Limit clamp current that flows through the I/O's internal diode

protection cells.

±20mA

Operating Junction Temperature ranges,

T

J

Commercial (default) 0°C to 90°C

Industrial (D suffix) -40°C to 90°C

Extended (A suffix) -40°C to 105°C

(1) Electrostatic discharge (ESD) to measure device sensitivity/immunity to damage caused by electrostatic discharges into the device.

(2) Level listed above is the passing level per ANSI/ESDA/JEDEC JS-001-2010. JEDEC document JEP 155 states that 500V HBM allows

safe manufacturing with a standard ESD control process, and manufacturing with less than 500V HBM is possible if necessary

precautions are taken. Pins listed as 1000V may actually have higher performance.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101E. JEDEC document JEP 157 states that 250V CDM allows safe

manufacturing with a standard ESD control process. Pins listed as 250V may actually have higher performance.

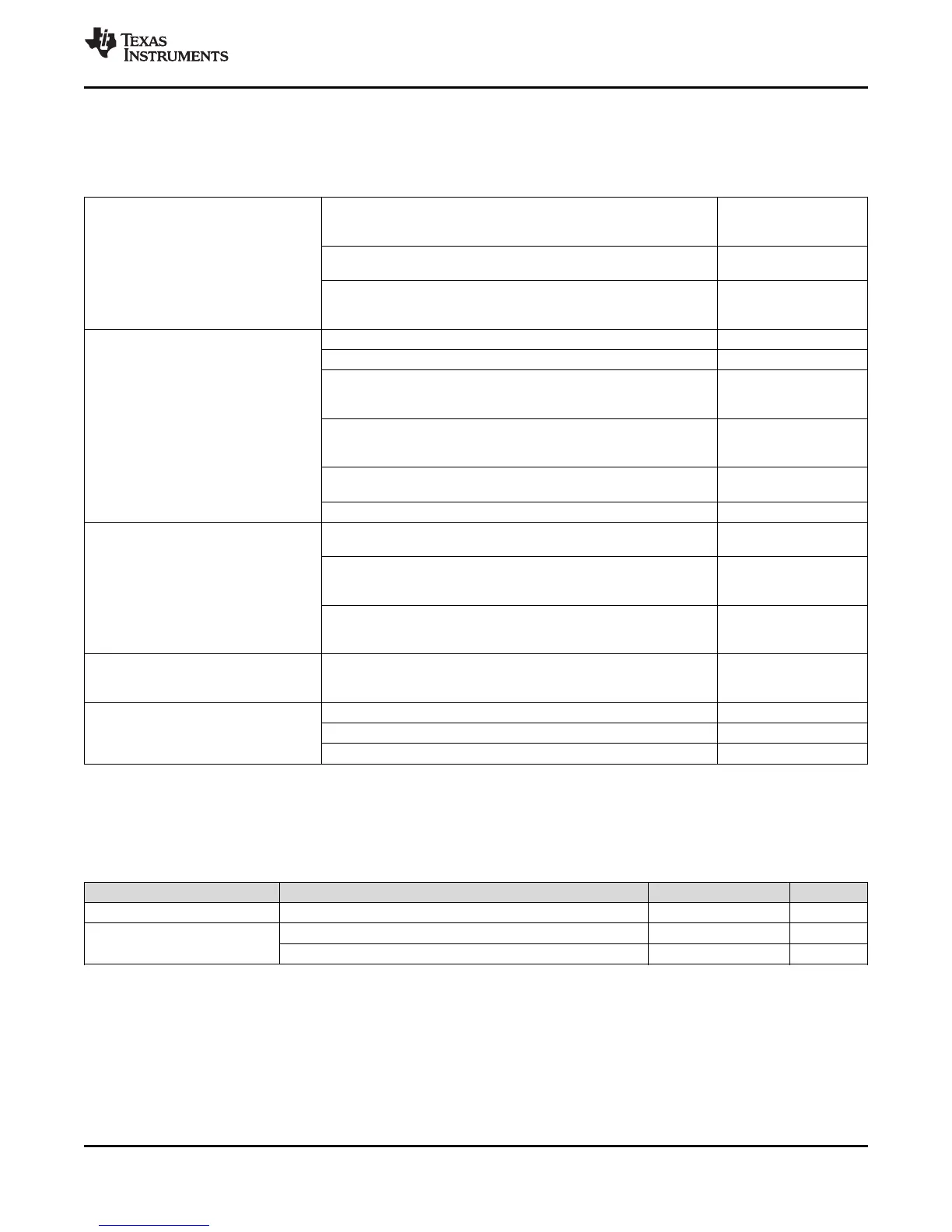

5.2 Handling Ratings

MIN MAX UNIT

Storage temperature range, T

stg

(default) -55 150 °C

ESD Stress Voltage, V

ESD

(1)

Human Body Model (HBM)

(2)

>1 >1 kV

Charged Device Model (CDM)

(3)

>500 >500 V

Loading...

Loading...