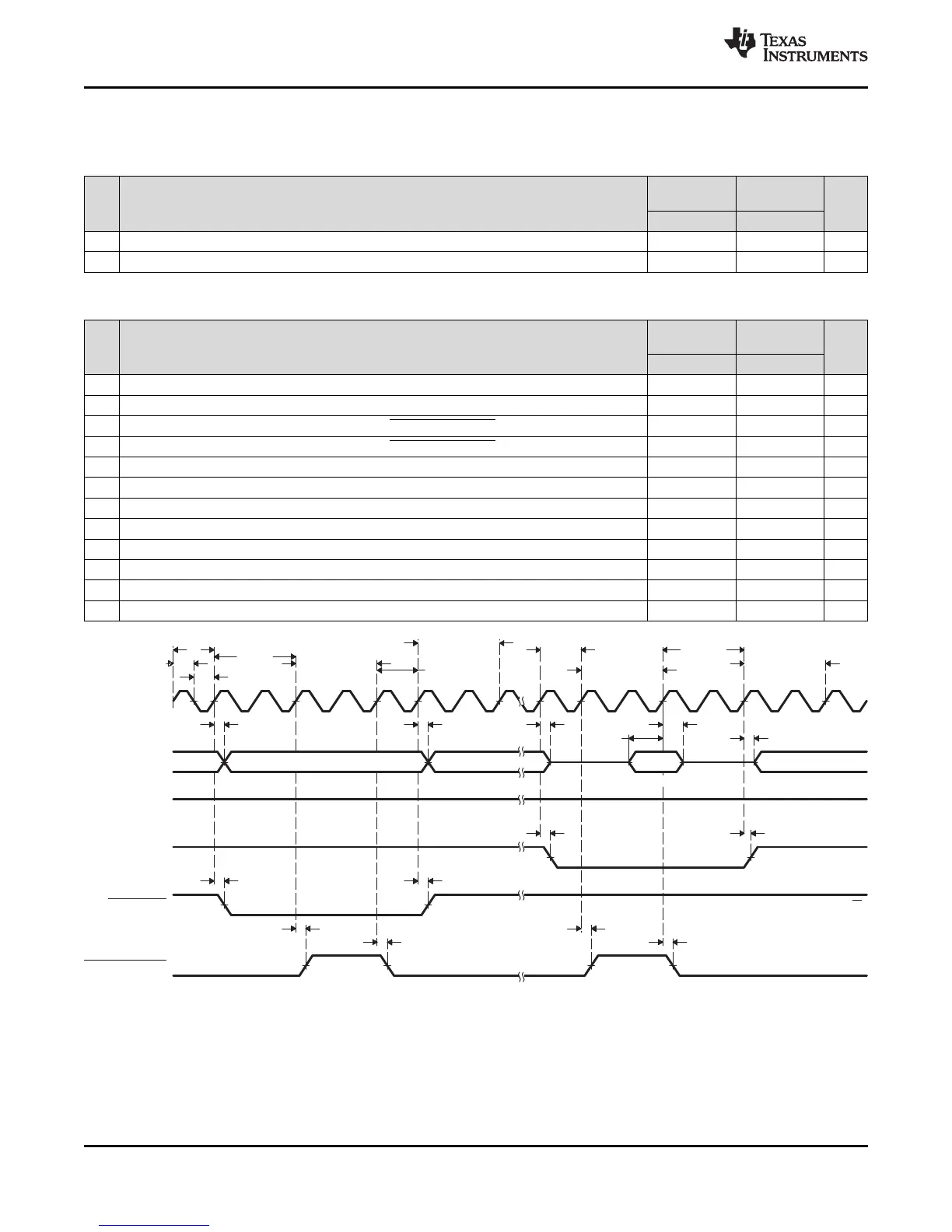

LCD_AC_ENB_CS

LCD_PCLK

2

3

1

W_SU

(0 to 31)

W_STROBE

(1 to 63)

W_HOLD

(1 to 15)

CS_DELAY

R_SU

(0 to 31)

R_STROBE

(1 to 63)

R_HOLD

(1 to 15)

CS_DELAY

LCD_MCLK

4

Write Data

5 14

16

17

15

Data[7:0]

Not Used

8 9

10 11

12

13

12

13

RS

R/W

E0

E1

LCD_D[15:0]

LCD_VSYNC

LCD_HSYNC

Read Status

206

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical Specifications Copyright © 2009–2017, Texas Instruments Incorporated

6.24.1 LCD Interface Display Driver (LIDD Mode)

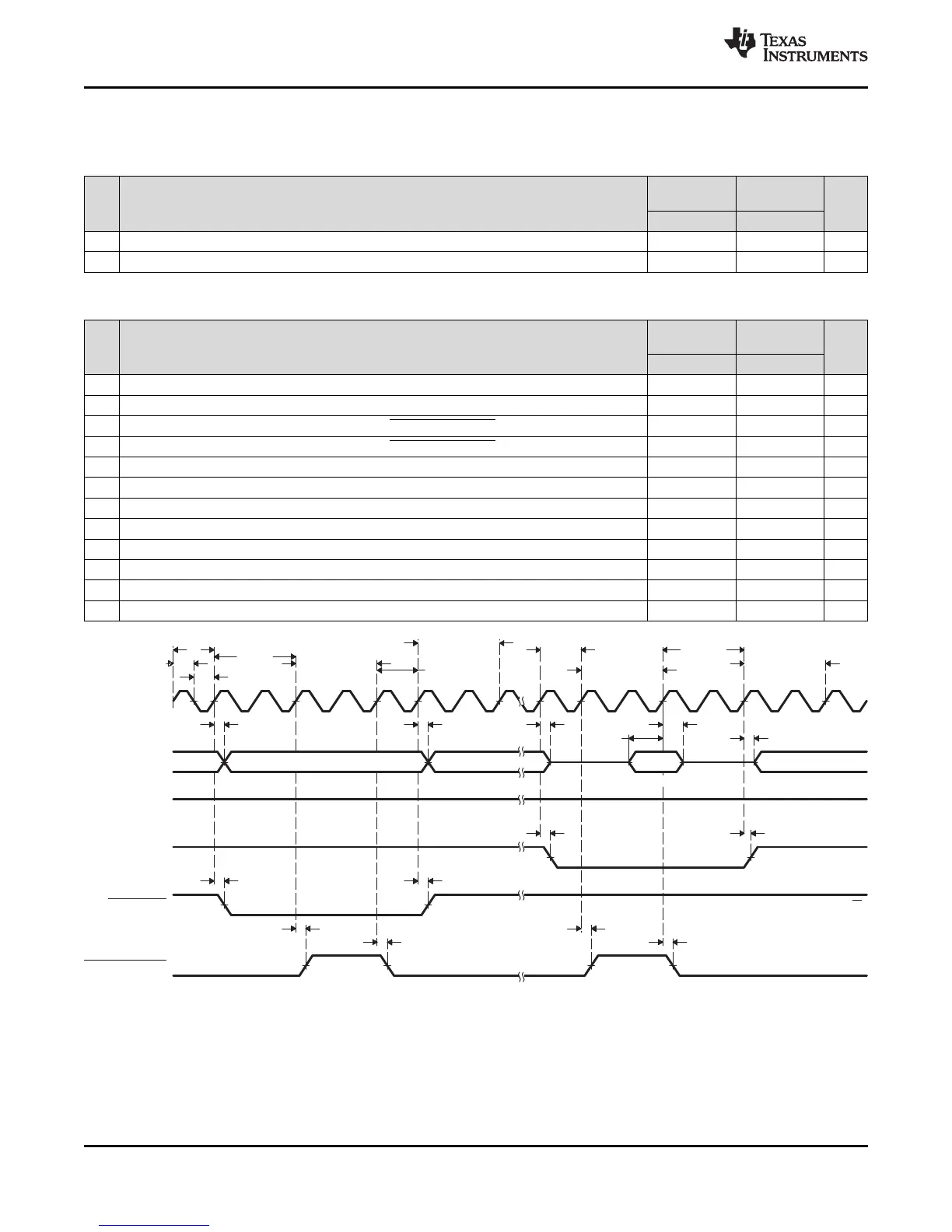

Table 6-108. Timing Requirements for LCD LIDD Mode

NO.

1.3V, 1.2V,

1.1V

1.0V

UNIT

MIN MAX MIN MAX

16 t

su(LCD_D)

Setup time, LCD_D[15:0] valid before LCD_MCLK high 7 8 ns

17 t

h(LCD_D)

Hold time, LCD_D[15:0] valid after LCD_MCLK high 0 0 ns

Table 6-109. Switching Characteristics Over Recommended Operating Conditions for LCD LIDD Mode

NO. PARAMETER

1.3V, 1.2V,

1.1V

1.0V

UNIT

MIN MAX MIN MAX

4 t

d(LCD_D_V)

Delay time, LCD_MCLK high to LCD_D[15:0] valid (write) 0 7 0 9 ns

5 t

d(LCD_D_I)

Delay time, LCD_MCLK high to LCD_D[15:0] invalid (write) 0 7 0 9 ns

6 t

d(LCD_E_A

) Delay time, LCD_MCLK high to LCD_AC_ENB_CS low 0 7 0 9 ns

7 t

d(LCD_E_I)

Delay time, LCD_MCLK high to LCD_AC_ENB_CS high 0 7 0 9 ns

8 t

d(LCD_A_A)

Delay time, LCD_MCLK high to LCD_VSYNC low 0 7 0 9 ns

9 t

d(LCD_A_I)

Delay time, LCD_MCLK high to LCD_VSYNC high 0 7 0 9 ns

10 t

d(LCD_W_A)

Delay time, LCD_MCLK high to LCD_HSYNC low 0 7 0 9 ns

11 t

d(LCD_W_I)

Delay time, LCD_MCLK high to LCD_HSYNC high 0 7 0 9 ns

12 t

d(LCD_STRB_A)

Delay time, LCD_MCLK high to LCD_PCLK active 0 7 0 9 ns

13 t

d(LCD_STRB_I)

Delay time, LCD_MCLK high to LCD_PCLK inactive 0 7 0 9 ns

14 t

d(LCD_D_Z)

Delay time, LCD_MCLK high to LCD_D[15:0] in 3-state 0 7 0 9 ns

15 t

d(Z_LCD_D)

Delay time, LCD_MCLK high to LCD_D[15:0] (valid from 3-state) 0 7 0 9 ns

Figure 6-54. Character Display HD44780 Write

Loading...

Loading...