22

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

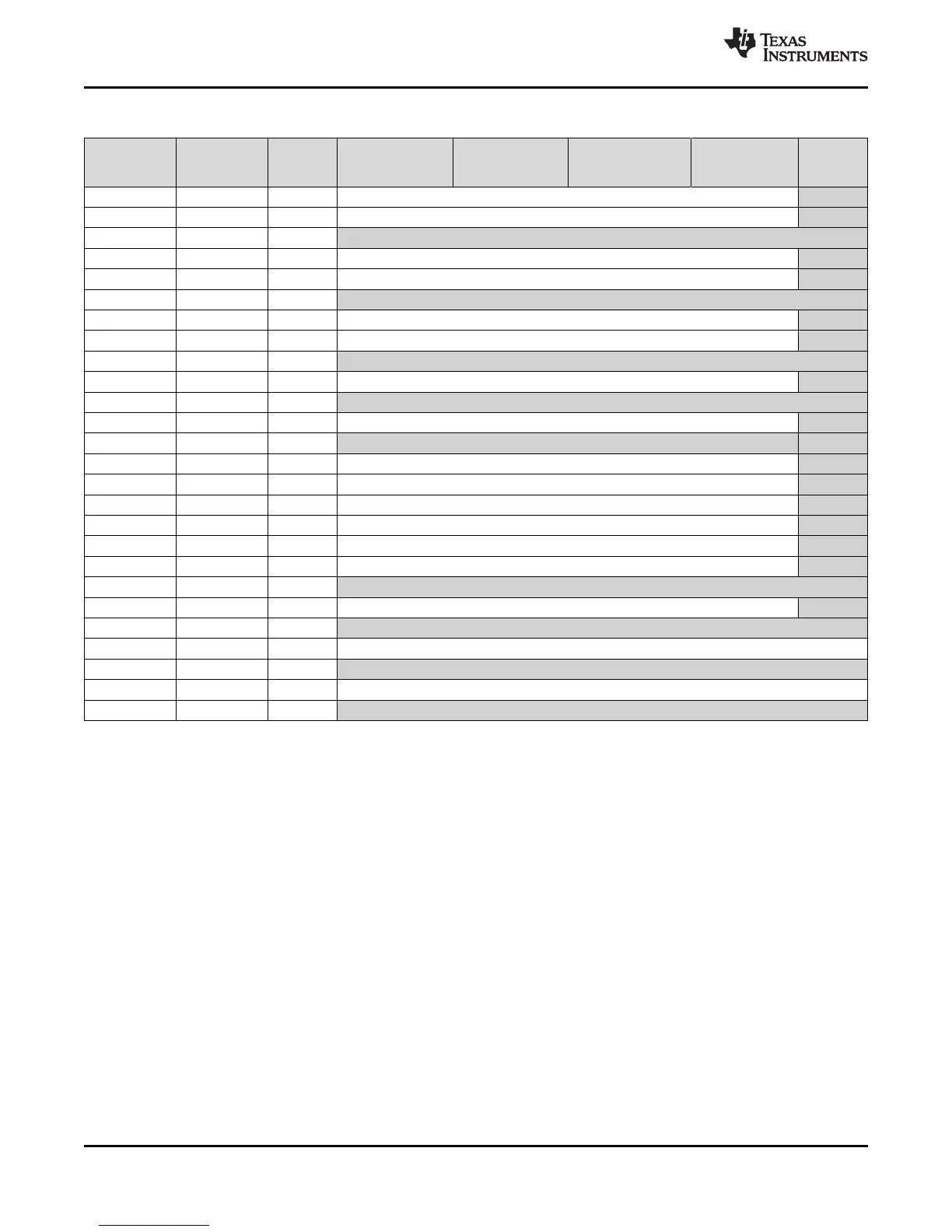

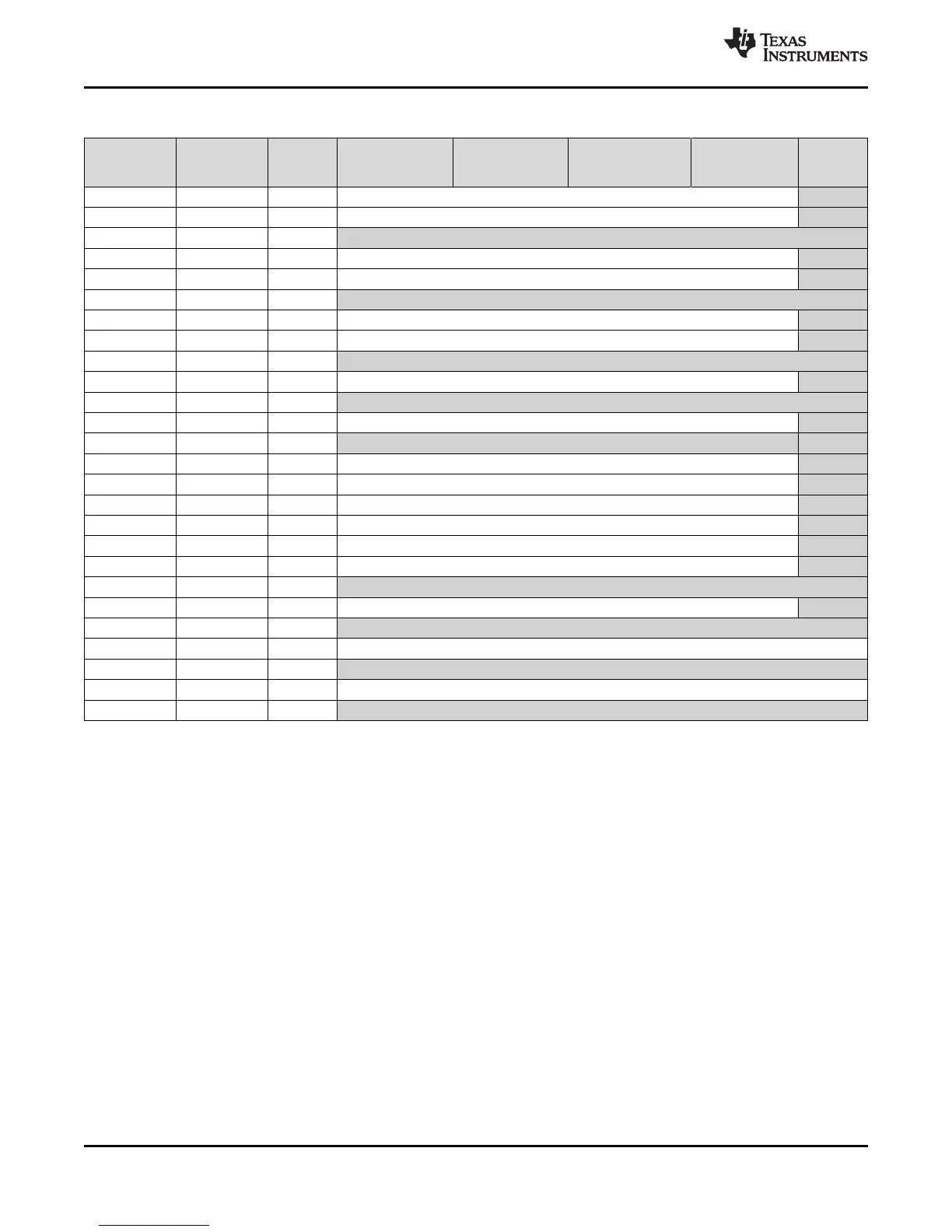

Table 3-4. C6748 Top Level Memory Map (continued)

Start Address End Address Size DSP Mem Map EDMA Mem Map PRUSS Mem Map Master

Peripheral Mem

Map

LCDC

Mem Map

0x01F0 D000 0x01F0 DFFF 4K Timer3

0x01F0 E000 0x01F0 EFFF 4K SPI1

0x01F0 F000 0x01F0 FFFF

0x01F1 0000 0x01F1 0FFF 4K McBSP0 FIFO Data

0x01F1 1000 0x01F1 1FFF 4K McBSP1 FIFO Data

0x01F1 2000 0x116F FFFF

0x1170 0000 0x117F FFFF 1024K DSP L2 ROM

(1)

0x1180 0000 0x1183 FFFF 256K DSP L2 RAM

0x1184 0000 0x11DF FFFF

0x11E0 0000 0x11E0 7FFF 32K DSP L1P RAM

0x11E0 8000 0x11EF FFFF

0x11F0 0000 0x11F0 7FFF 32K DSP L1D RAM

0x11F0 8000 0x3FFF FFFF

0x4000 0000 0x5FFF FFFF 512M EMIFA SDRAM data (CS0)

0x6000 0000 0x61FF FFFF 32M EMIFA async data (CS2)

0x6200 0000 0x63FF FFFF 32M EMIFA async data (CS3)

0x6400 0000 0x65FF FFFF 32M EMIFA async data (CS4)

0x6600 0000 0x67FF FFFF 32M EMIFA async data (CS5)

0x6800 0000 0x6800 7FFF 32K EMIFA Control Regs

0x6800 8000 0x7FFF FFFF

0x8000 0000 0x8001 FFFF 128K On-chip RAM

0x8002 0000 0xAFFF FFFF

0xB000 0000 0xB000 7FFF 32K DDR2/mDDR Control Regs

0xB000 8000 0xBFFF FFFF

0xC000 0000 0xCFFF FFFF 256M DDR2/mDDR Data

0xD000 0000 0xFFFF FFFF

Loading...

Loading...