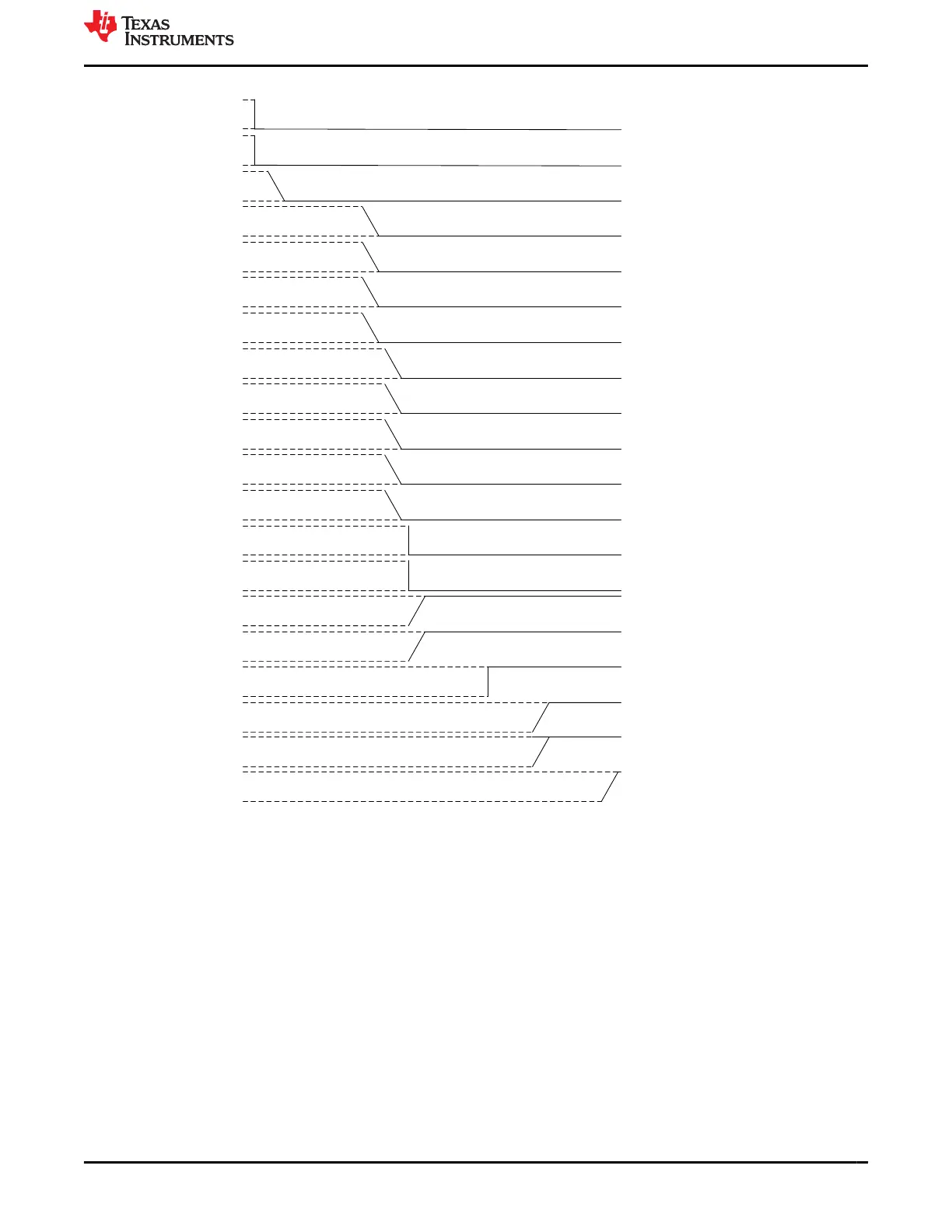

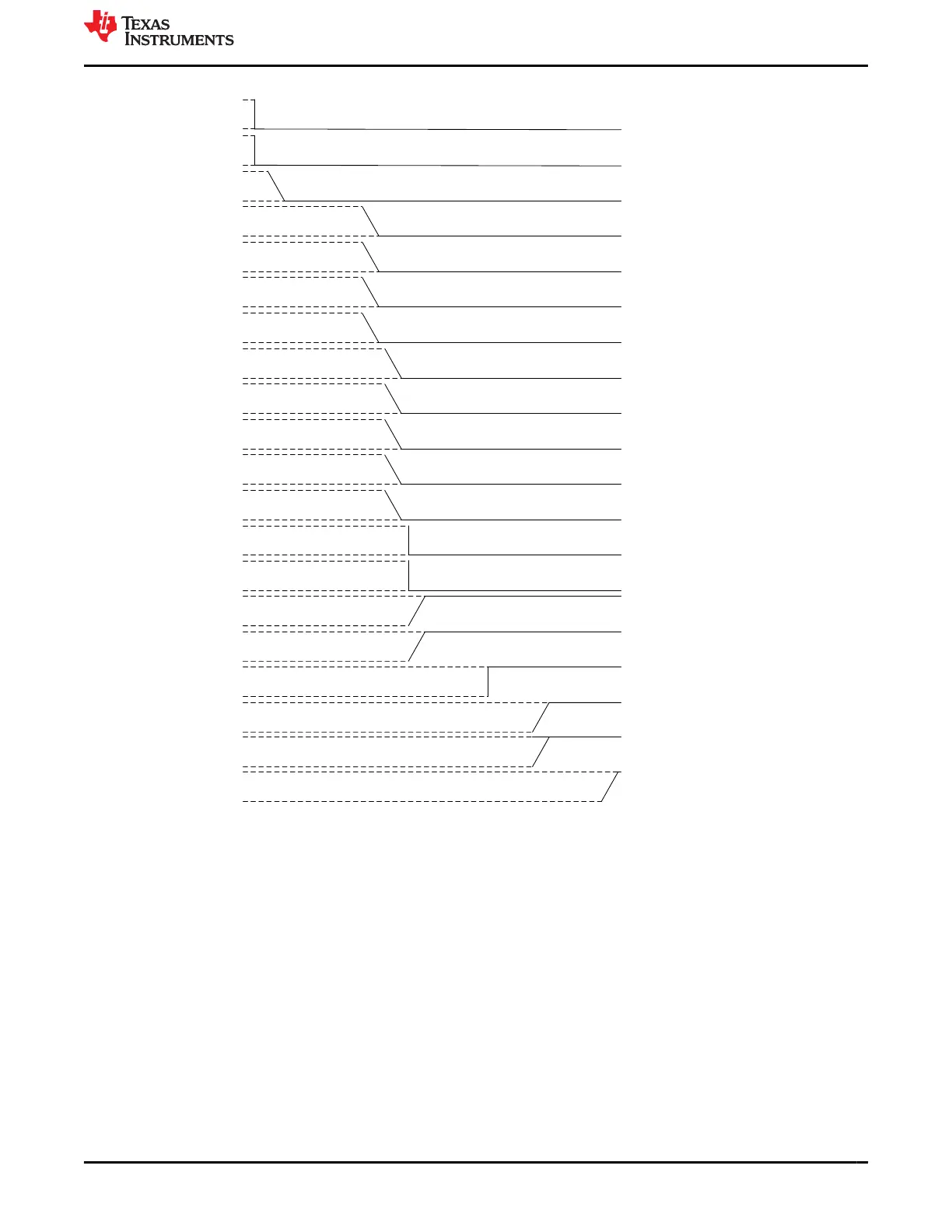

Resource PMIC Delay Diagram Total Delay Rail Name

GPIO9

TPS65941120-Q1

(Leo A)

3500 us EN_MCU3V3_VIO

LDO4

TPS65941120-Q1

(Leo A)

3000 us VDA_MCU_1V8

LDO3

TPS65941120-Q1

(Leo A)

3000 us VDD_MCUIO_1V8

BUCK5

TPS65941120-Q1

(Leo A)

2500 us VDD_MCU_0V85

nRSTOUT

TPS65941120-Q1

(Leo A)

0 us H_MCU_PORz

FSM I2C Trigger

GPIO11

(nRSTOUT_SOC)

TPS65941120-Q1

(Leo A)

0 us H_SOC_PORz

BUCK5

TPS65941421-Q1

(Leo B)

500 us VDD_RAM_0V85

LDO3

TPS65941421-Q1

(Leo B)

2500 us VDA_DLL_0V8

BUCK1234

LP876411B5-Q1

(Hera C)

2500 us VDD_CORE_0V8

BUCK1234

TPS65941120-Q1

(Leo A)

2500 us VDD_CPU_AVS

LDO4

TPS65941421-Q1

(Leo B)

3000 us VDD_PLL_1V8

BUCK1

TPS65941421-Q1

(Leo B)

3000 us VDD_IO_1V8

BUCK3

TPS65941421-Q1

(Leo B)

3000 us VDD_PHY_1V8

GPIO11

TPS65941421-Q1

(Leo B)

3500 us EN_3V3_VIO

LDO2

TPS65941120-Q1

(Leo A)

3500 us

VDD_MCU_

GPIORET_3V3

LDO2

TPS65941421-Q1

(Leo B)

3500 us VDD_GPIORET_3V3

GPIO3

TPS65941421-Q1

(Leo B)

5200 us EN_DDR_VDD1

I2C_6 = 1

I2C_7 = 1

I2C_5 = 1

LDO1

TPS65941120-Q1

(Leo A)

6200 us VDD_MCU_WK_0V8

LDO1

TPS65941421-Q1

(Leo B)

6200 us VDD_WK_0V8

BUCK4

TPS65941421-Q1

(Leo B)

8200 us VDD_DDR_1V1

I2C_7 = 1

I2C_6 = 1

I2C_5 = 1

Figure 6-13. TO_RETENTION when I2C triggers are high in both PMICs

At the end of the sequence, both PMICs set the LPM_EN and clear the CLKMON_EN and AMUXOUT_EN.

The TPS65941120 device also performs an additional 16 ms delay based upon the contents of the register

(PFSM_DELAY_REG_2) to ensure that the TPS65941120 sequence finishes last.

www.ti.com Pre-Configurable Finite State Machine (PFSM) Settings

SLVUCJ9 – FEBRUARY 2023

Submit Document Feedback

TPS65941120-Q1, TPS65941421-Q1 and LP876411B5-Q1 PMIC User Guide

for J721S2, PDN-0A

49

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...