7 Application Examples

This section provides examples of how to interact with the PMICs from the perspective of the MCU and over I

2

C.

Table 7-1 shows how the I

2

C commands are presented in the following sections. These examples, when used in

conjunction with the data sheet, can be generalized and applied to other use cases.

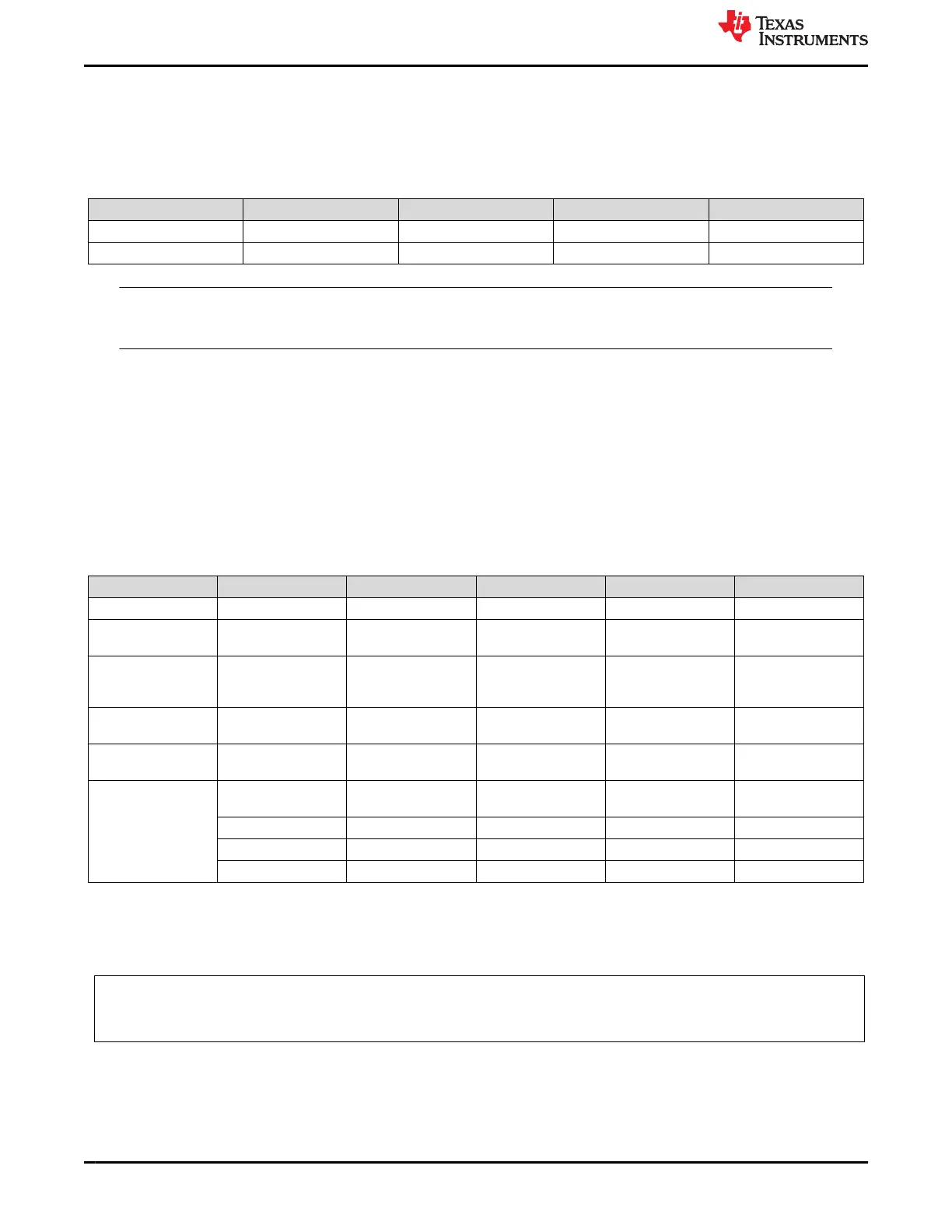

Table 7-1. I

2

C Instruction Format

I

2

C Address Register Address Data Mask

Write 0x48, 0x4C or 0x58 0x00 - 0xFF 0x00 - 0xFF 0x00 - 0xFF

Read 0x48, 0x4C or 0x58 0x00 - 0xFF NA NA

Note

When the MASK is non-zero, this assumes a read has taken place and then a logical operation

applied to only change the desired bit fields before writing the data back.

7.1 Moving Between States; ACTIVE and RETENTION

The default configuration of the NVM transitions the PMICs to the ACTIVE state when the ENABLE pin on the

TPS65941120 goes high (rising edge triggered). The nINT pin goes low to indicate to the MCU that interrupts

have occurred in the PMICs. After a normal power up sequence the interrupts are the ENABLE_INT and

BIST_PASS_INT. The ENABLE_INT prohibits the PMICs from processing any lower priority triggers below the

'ON Request' in Table 6-1. The blocking of the lower priority triggers is why the PMICs are in the ACTIVE state

even though the NSLEEP1 and NSLEEP2 bits are both cleared. Once the ENABLE_INT is cleared the state is

defined by Table 7-2. The following sections describe the I

2

C commands for transitioning between the different

states.

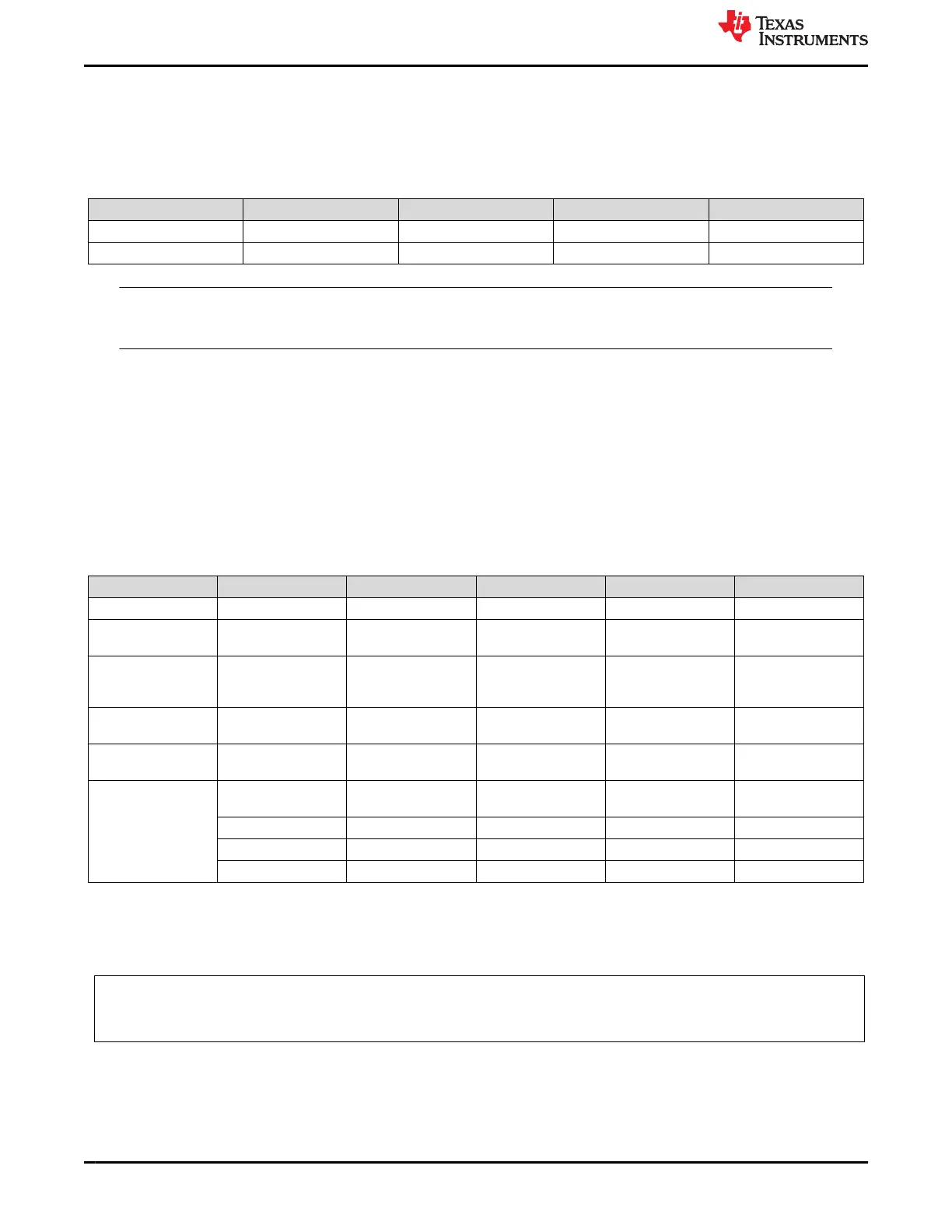

Table 7-2. State Table

NSLEEP1 NSLEEP2 I2C_7 I2C_6 I2C_5 State

1 1 NA NA NA ACTIVE

0 1 0 0 NA MCU ONLY without

DDR Retention

0 1 1 1 NA MCU ONLY with DDR

Retention and Main

GPIO Retention

0 1 1 0 NA MCU ONLY with DDR

Retention

0 1 0 1 NA MCU ONLY with Main

GPIO Retention

Do not Care 0 1 1 1 DDR Retention with

GPIO Retention

0 0 1 1 GPIO Retention

0 1 0 0 DDR Retention

0 0 0 0 Retention

7.1.1 ACTIVE

In this example the, PMIC is already in the ACTIVE state after a normal power up event. The PMIC is kept in the

ACTIVE state by setting the NSLEEP1 and NSLEEP2 bits before clearing the ENABLE_INT.

Write 0x48:0x86:0x03:0xFC // Set NSLEEP1 and NSLEEP2 in TPS65951213

Write 0x48:0x66:0x01:0xFE // Clear BIST_PASS_INT

Write 0x48:0x65:0x26:0xD9 // Clear all potential sources of the On Request

Application Examples www.ti.com

50 TPS65941120-Q1, TPS65941421-Q1 and LP876411B5-Q1 PMIC User Guide

for J721S2, PDN-0A

SLVUCJ9 – FEBRUARY 2023

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...