ProTechTPS Total Protection System Manual 26710V1

90 Woodward

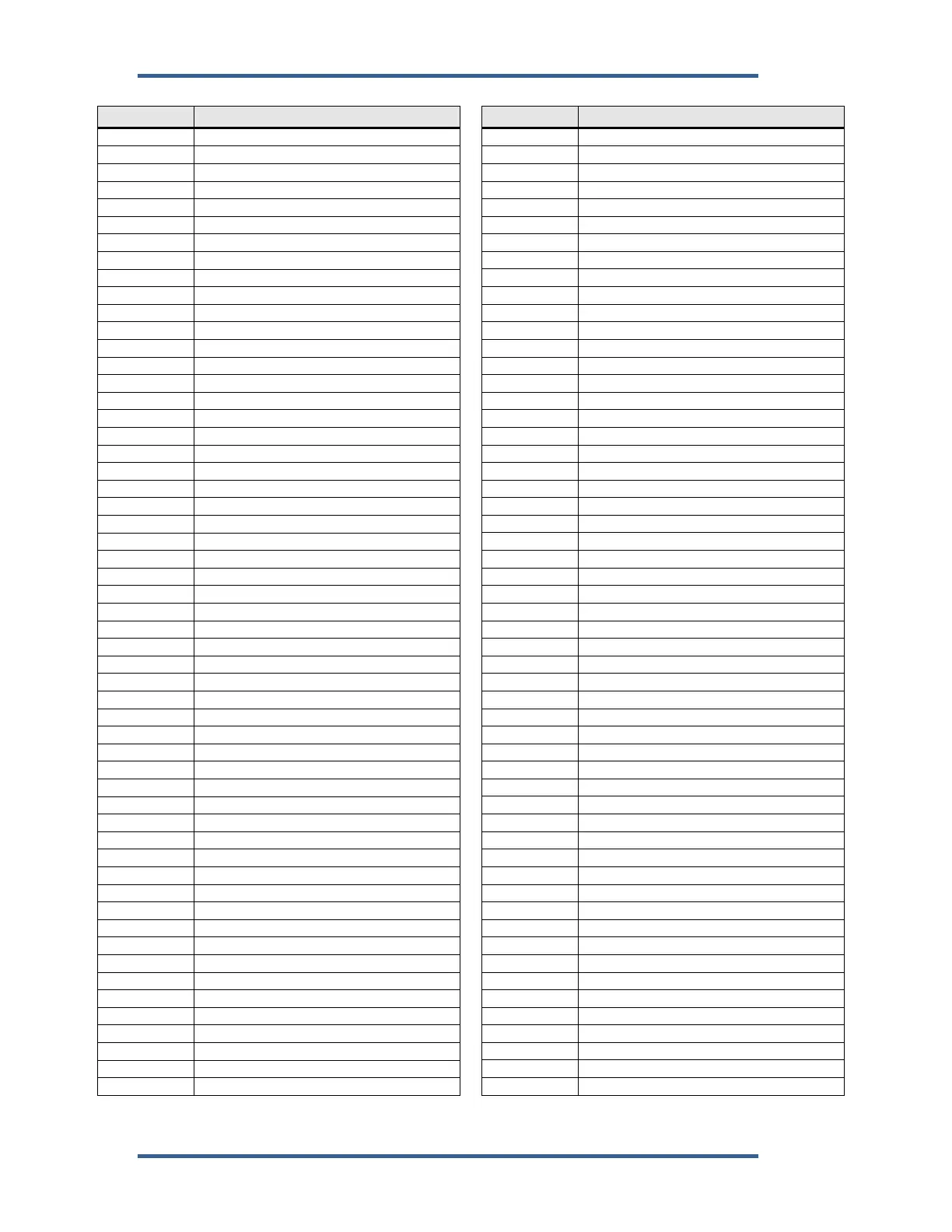

Table 4-5. Boolean Read Addresses (Code 02)

ADDRESS DESCRIPTION

1:0001 Internal Fault Trip

1:0002 Power Up Trip

1:0003 Configuration Trip

1:0004 Parameter Error Trip

1:0005 Over Speed Trip

1:0006 Over Accel Trip

1:0007 Speed Redundancy Manager Trip

1:0008 Speed Probe Open Wire Trip

1:0009 Speed Lost Trip

1:0010 Speed Fail Trip

1:0011 Speed Fail Timeout Trip

1:0012 Resettable Trip Input Trip

1:0013 to 0037 User Configurable Trips 1 to 25

1:0101 to 0137 Trip Latch First Outs 1 to 37

1:0201 Internal Fault Alarm

1:0202 Module Config Mismatch Alarm

1:0203 Power Supply 1 Fault Alarm

1:0204 Power Supply 2 Fault Alarm

1:0205 Speed Fail Alarm

1:0206 Speed Lost Alarm

1:0207 Speed Probe Open Wire Alarm

1:0208 Speed Red Mgr Input Difference Alarm

1:0209 Speed Red Mgr Input 1 Invalid Alarm

1:0210 Speed Red Mgr Input 2 Invalid Alarm

1:0211 Speed Red Mgr Input 3 Invalid Alarm

1:0212 Temp Overspeed SP is Active Alarm

1:0213 Simulated Speed Test in Progress Alarm

1:0214 Auto Speed Test Active Alarm

1:0215 Auto Speed Test Failed Alarm

1:0216 Auto Sequence Test Active Alarm

1:0217 Auto Sequence Continue Timeout Alarm

1:0218 User Test 1 Active Alarm

1:0219 User Test 2 Active Alarm

1:0220 User Test 3 Active Alarm

1:0221 Trip Cycle Time Mon 1 Alarm

1:0222 Trip Cycle Time Mon 2 Alarm

1:0223 Trip Latch Output Alarm

1:0224 to 0298 User Configurable Alarms 1 to 75

1:0401 to 0425 Event Latched Inputs 1 to 25

1:0501 to 0525 Event Latch First Outs 1 to 25

1:1001 Speed Fail Override

1:1002 Overspeed

1:1003 Over-acceleration

1:1004 Speed Fail Trip Non-Latched

1:1005 Speed Fail Timeout

1:1006 Speed Lost Alarm Non-Latched

1:1007 Speed Lost Trip Non-Latched

1:1008 Speed Probe Open Wire Trip Non-Latched

1:1009 Tmp Ovrspd Setpoint On

1:1010 Simulated Speed Active

1:1011 Auto Speed Test Active

1:1012 Auto Speed Test Failed

1:1013 Auto Sequence Test Active

1:1014 Auto Sequence Continue Timeout

1:1015 User Defined Test 1

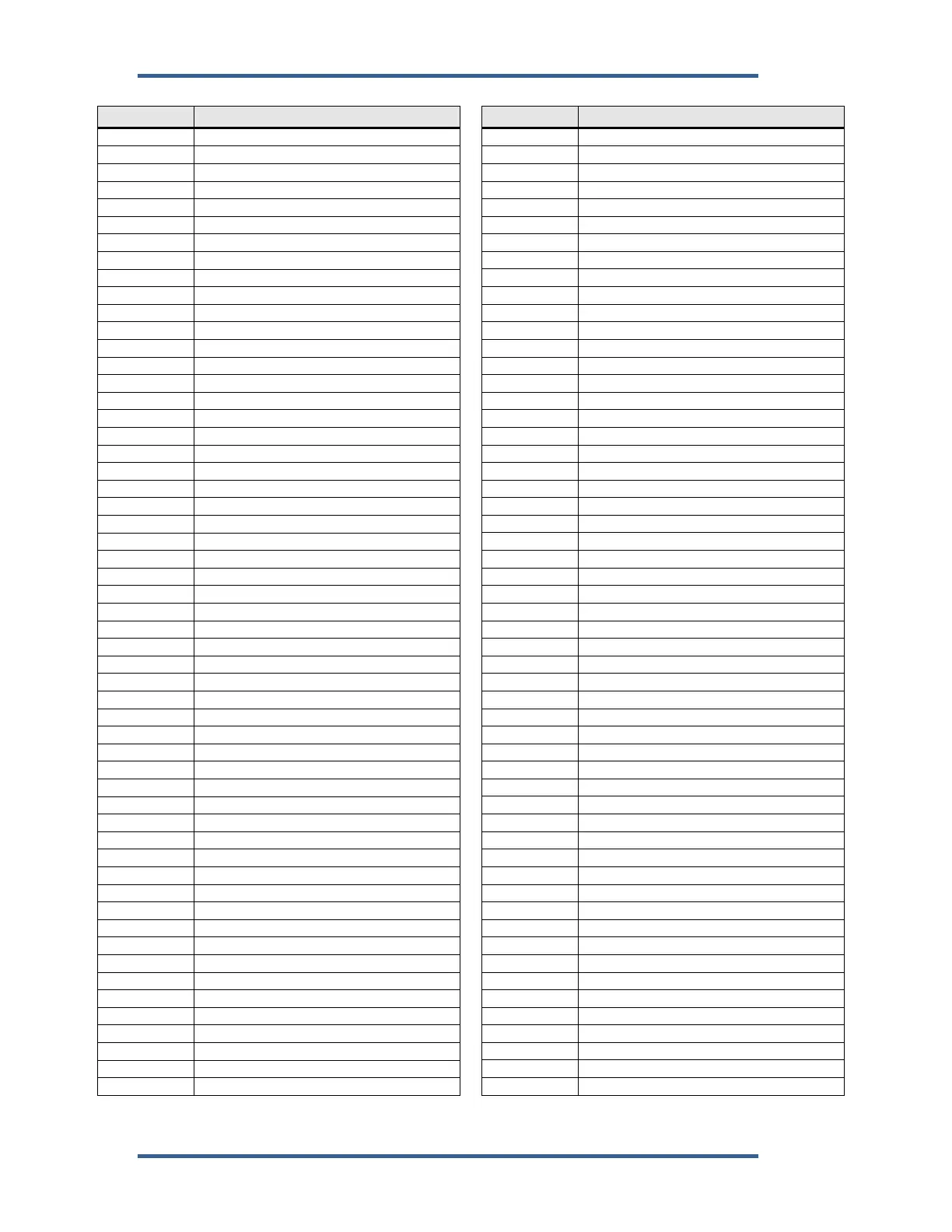

ADDRESS DESCRIPTION

1:1016 User Defined Test 2

1:1017 User Defined Test 3

1:1018 Configuration Mismatch

1:1019 Speed Fail Alarm Non-Latched

1:1020 Trip Latch Output

1:1021 Alarm Latch Output

1:1022 Event Latch Output

1:1023 Discrete Input 1

1:1024 Discrete Input 2

1:1025 Discrete Input 3

1:1026 Discrete Input 4

1:1027 Discrete Input 5

1:1028 Discrete Input 6

1:1029 Discrete Input 7

1:1030 Discrete Input 8

1:1031 Discrete Input 9

1:1032 Discrete Input 10

1:1033 Analog Input 1 Hi

1:1034 Analog Input 2 Hi

1:1035 Analog Input 3 Hi

1:1036 Analog Input 4 Hi

1:1037 Analog Input 5 Hi

1:1038 Analog Input 6 Hi

1:1039 Analog Input 7 Hi

1:1040 Analog Input 8 Hi

1:1041 Analog Input 9 Hi

1:1042 Analog Input 10 Hi

1:1043 Analog Input 1 HiHi

1:1044 Analog Input 2 HiHi

1:1045 Analog Input 3 HiHi

1:1046 Analog Input 4 HiHi

1:1047 Analog Input 5 HiHi

1:1048 Analog Input 6 HiHi

1:1049 Analog Input 7 HiHi

1:1050 Analog Input 8 HiHi

1:1051 Analog Input 9 HiHi

1:1052 Analog Input 10 HiHi

1:1053 Analog Input 1 Lo

1:1054 Analog Input 2 Lo

1:1055 Analog Input 3 Lo

1:1056 Analog Input 4 Lo

1:1057 Analog Input 5 Lo

1:1058 Analog Input 6 Lo

1:1059 Analog Input 7 Lo

1:1060 Analog Input 8 Lo

1:1061 Analog Input 9 Lo

1:1062 Analog Input 10 Lo

1:1063 Analog Input 1 LoLo

1:1064 Analog Input 2 LoLo

1:1065 Analog Input 3 LoLo

1:1066 Analog Input 4 LoLo

1:1067 Analog Input 5 LoLo

1:1068 Analog Input 6 LoLo

1:1069 Analog Input 7 LoLo

1:1070 Analog Input 8 LoLo

Loading...

Loading...