ML505/ML506/ML507 Evaluation Platform www.xilinx.com 51

UG347 (v3.1.1) October 7, 2009

Detailed Description

R

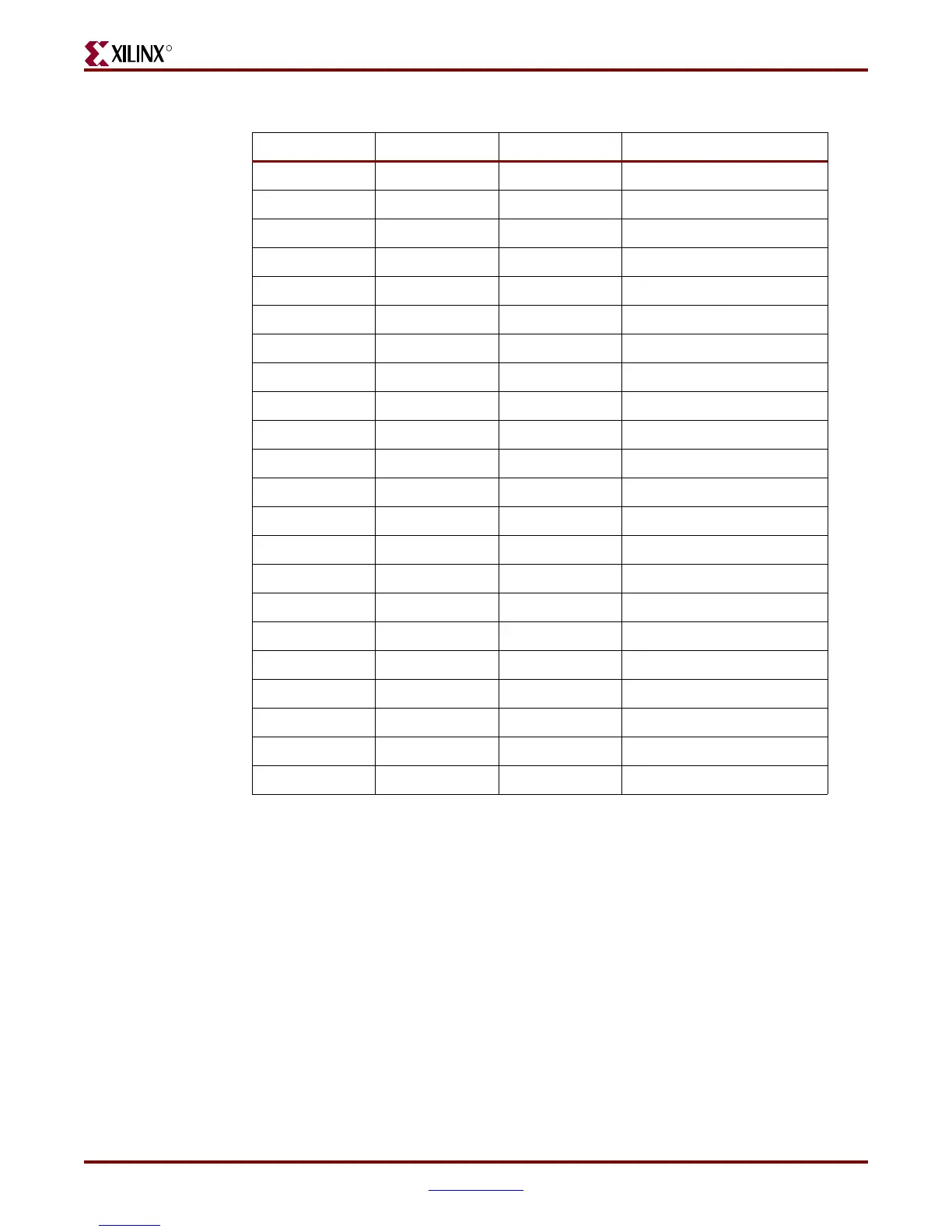

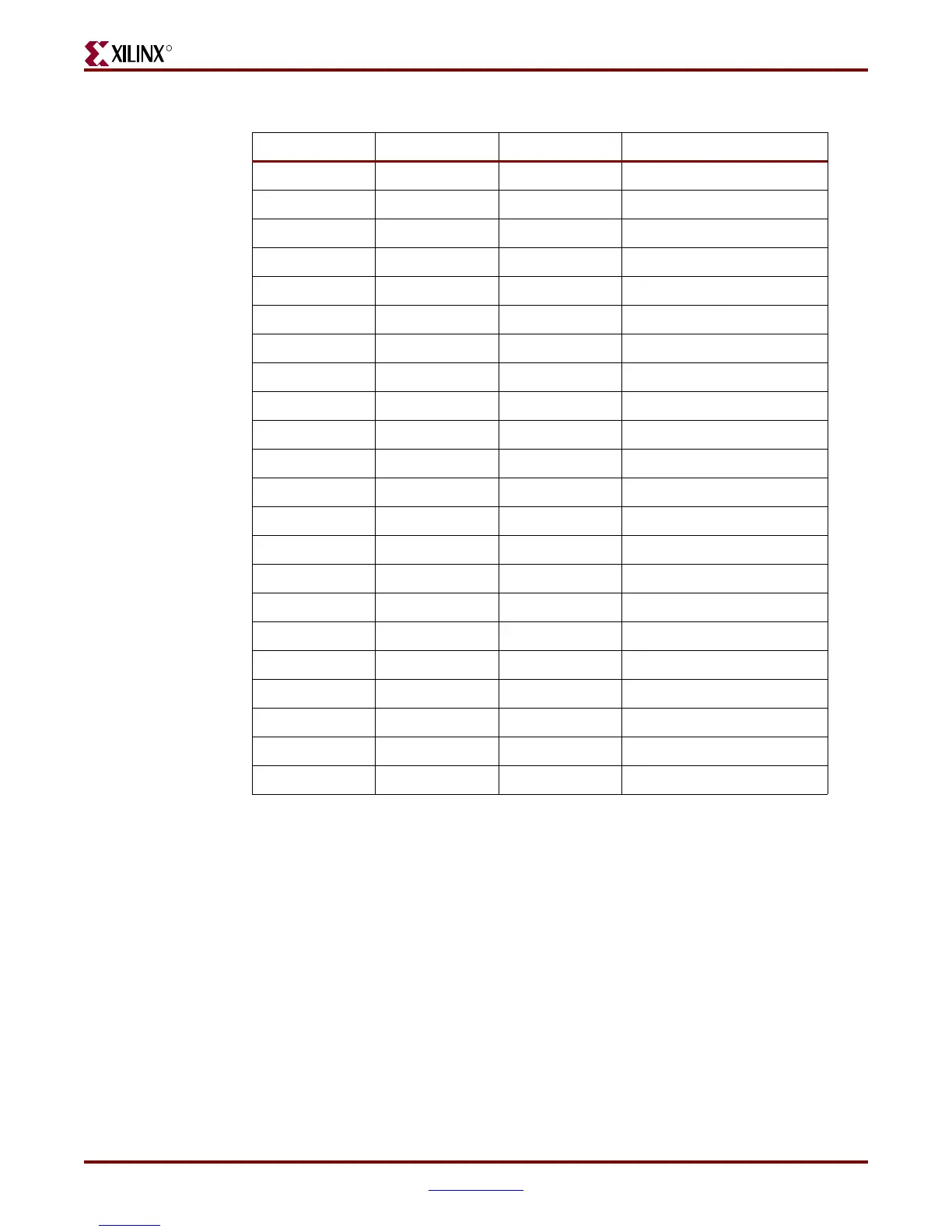

VAUXN[5] Y34 J6-30 HDR1_30

VAUXP[5] AA34 J6-26 HDR1_26

VAUXN[6] AA33 J4-38 HDR2_38_SM_6_N

VAUXP[6] Y33 J4-40 HDR2_40_SM_6_P

VAUXN[7] V34 J4-34 HDR2_34_SM_15_N

VAUXP[7] W34 J4-36 HDR2_36_SM_15_P

VAUXN[8] V33 J4-30 HDR2_30_DIFF_3_N

VAUXP[8] V32 J4-32 HDR2_32_DIFF_3_P

VAUXN[9] U31 J4-26 HDR2_26_SM_11_N

VAUXP[9] U32 J4-28 HDR2_28_SM_11_P

VAUXN[10] T34 J4-22 HDR2_22_SM_10_N

VAUXP[10] U33 J4-24 HDR2_24_SM_10_P

VAUXN[11] R32 J4-18 HDR2_18_DIFF_2_N

VAUXP[11] R33 J4-20 HDR2_20_DIFF_2_P

VAUXN[12] R34 J4-14 HDR2_14_DIFF_1_N

VAUXP[12] T33 J4-16 HDR2_16_DIFF_1_P

VAUXN[13] N32 J4-10 HDR2_10_DIFF_0_N

VAUXP[13] P32 J4-12 HDR2_12_DIFF_0_P

VAUXN[14] K32 J4-6 HDR2_6_SM_7_N

VAUXP[14] K33 J4-8 HDR2_8_SM_7_P

VAUXN[15] K34 J4-2 HDR2_2_SM_8_N

VAUXP[15] L34 J4-4 HDR2_4_SM_8_P

Table 1-34: System Monitor Connections (Cont’d)

External Input FPGA Pin Header Pin Schematic Net Name

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...