38 www.xilinx.com ML505/ML506/ML507 Evaluation Platform

UG347 (v3.1.1) October 7, 2009

Chapter 1: ML505/ML506/ML507 Evaluation Platform

R

37. JTAG Trace/Debug

CPU Debug Description

External-debug mode can be used to alter normal program execution. It provides the

ability to debug both system hardware and software. External-debug mode supports

setting of multiple breakpoints, as well as monitoring processor status. Access to processor

debugging resources is available through the CPU JTAG port (J51) providing the

appropriate connections to the FPGA fabric are in place.

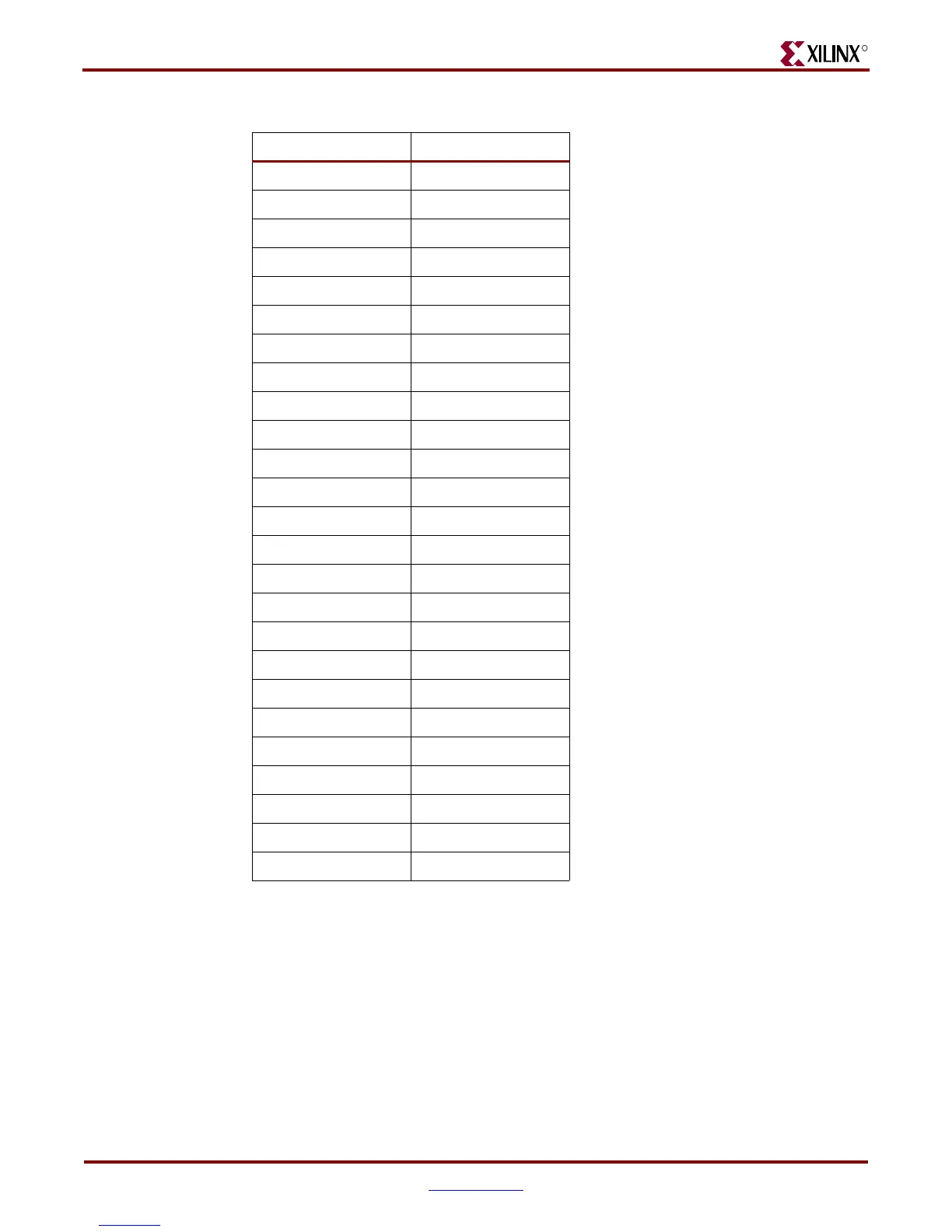

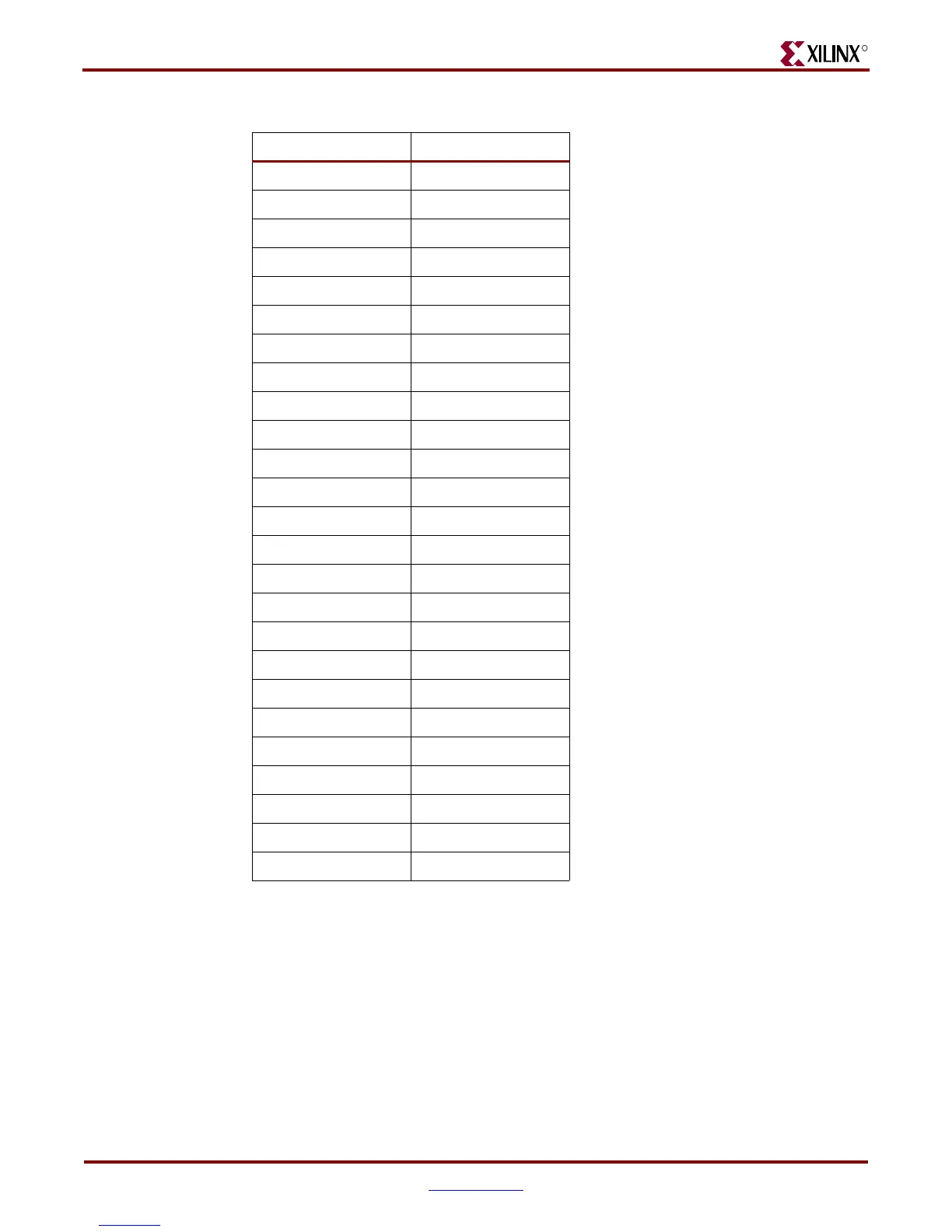

VGA_IN_RED5 AG6

VGA_IN_RED6 Y11

VGA_IN_RED7 W11

VGA_IN_GREEN0 Y8

VGA_IN_GREEN1 Y9

VGA_IN_GREEN2 AD4

VGA_IN_GREEN3 AD5

VGA_IN_GREEN4 AA6

VGA_IN_GREEN5 Y7

VGA_IN_GREEN6 AD6

VGA_IN_GREEN7 AE6

VGA_IN_BLUE0 AC4

VGA_IN_BLUE1 AC5

VGA_IN_BLUE2 AB6

VGA_IN_BLUE3 AB7

VGA_IN_BLUE4 AA5

VGA_IN_BLUE5 AB5

VGA_IN_BLUE6 AC7

VGA_IN_BLUE7 AD7

VGA_IN_CLAMP AH7

VGA_IN_COAST AG7

VGA_IN_EVEN_B W6

VGA_IN_VSOUT Y6

VGA_IN_HSOUT AE7

VGA_IN_SOGOUT AF6

Table 1-20: VGA Interface Connections (Cont’d)

Net Name FPGA Pin

Downloaded from Elcodis.com electronic components distributor

Loading...

Loading...