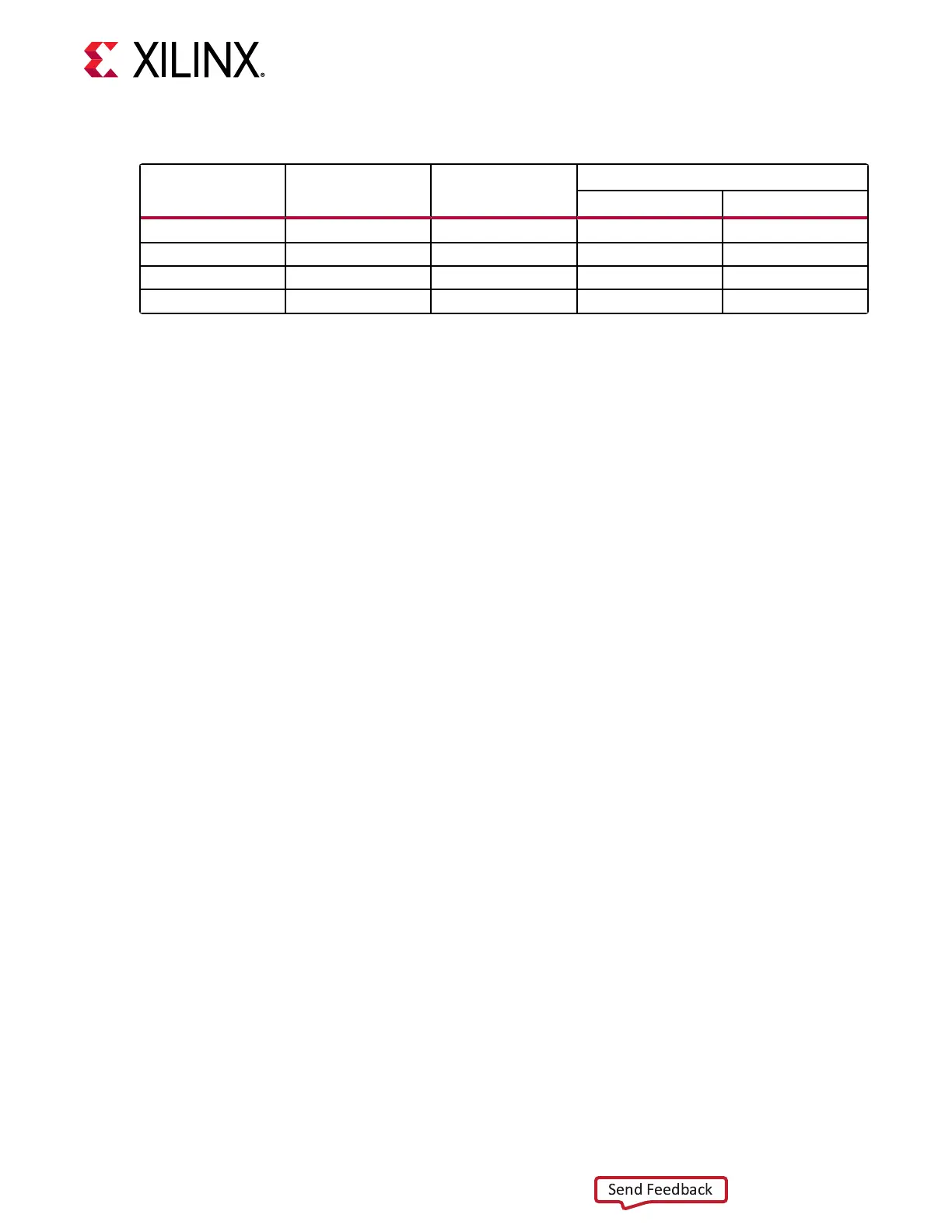

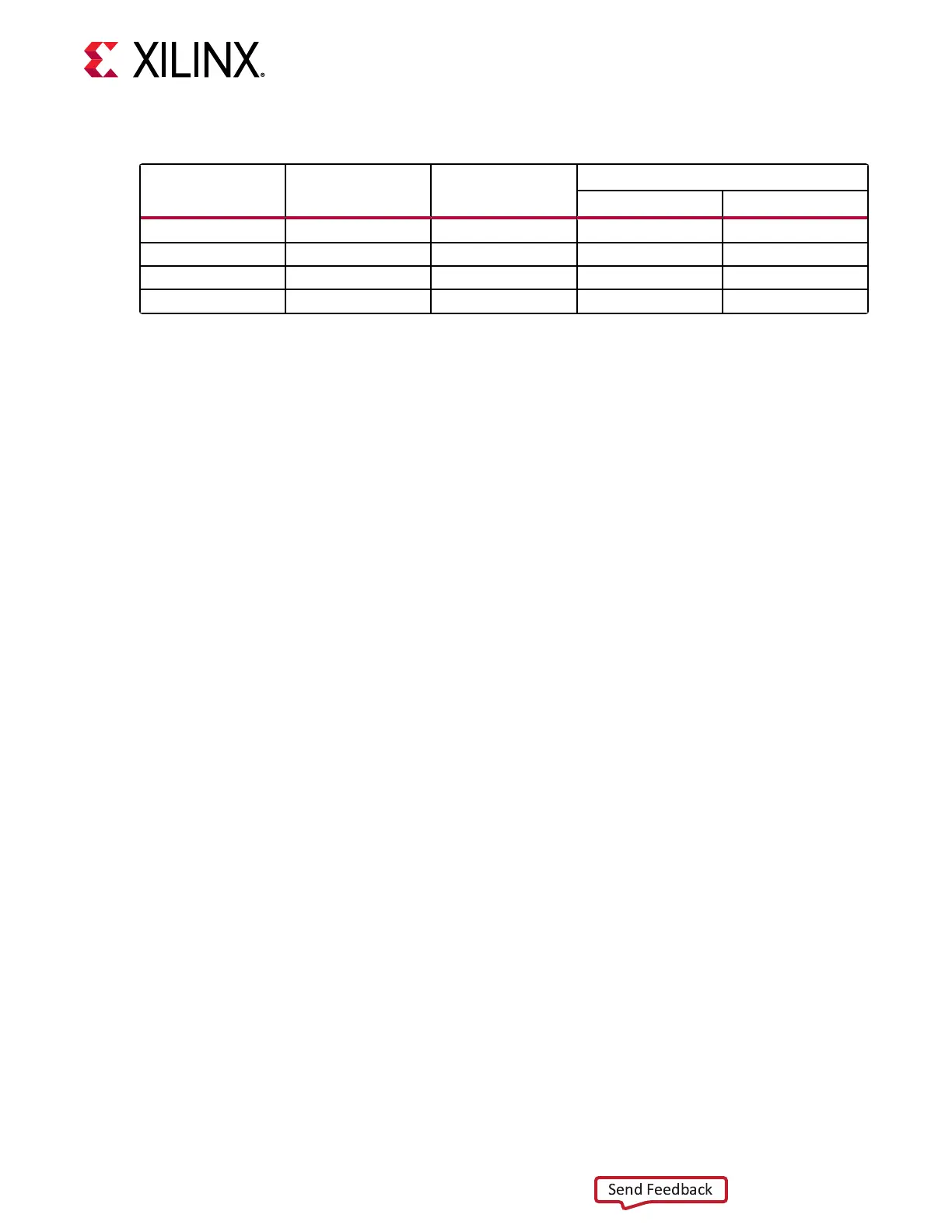

Table 24: M.2 U40 Connections to the XCZU48DR Zynq UltraScale+ RFSoC

XCZU48DR (U1) Pin Net Name I/O Standard

M.2 Connector U40

Pin Number Pin Name

AD36 GT3_SATA1_TX_P 1 49 SATA-A+

AD37 GT3_SATA1_TX_N 1 47 SATA-A-

AC38 GT3_SATA1_RX_P 1 41 SATA-B+

AC39 GT3_SATA1_RX_N 1 43 SATA-B-

Notes:

1. Series capacitor coupled, MGT I/F and I/O standards do not apply.

For more informaon, see PCI_Express_M.2_Specicaon_Rev1.1_TS_12092016_NCB on the

PCI-SIG website.

The detailed RFSoC connecons for the feature described in this secon are documented in the

ZCU208 board XDC le, referenced in Appendix B: Xilinx Design Constraints.

FPGA Mezzanine Card Interface

The ZCU208 evaluaon board supports the VITA 57.4 FPGA mezzanine card plus (FMC+ or

FMCP) specicaon by providing a subset implementaon of the high pin count connector at J28

(HSPC). FMC+ connectors use a 14 x 40 form factor, populated with 560 pins. The connector is

keyed so that a mezzanine card, when installed on the ZCU208 evaluaon board, faces away

from the board.

FMCP Connector J28

Samtec SEAF series, 1.27 mm (0.050 in) pitch. Mates with SEAM series connector. More

informaon about SEAF series connectors is available on the Samtec, Inc. website. More

informaon about the VITA 57.4 FMC+ specicaon is available on the VITA FMC Markeng

Alliance website.

The 560-pin FMC+ connector dened by the FMC specicaon (see Appendix A: VITA57.4

FMCP Connector Pinout) provides connecvity for up to:

• 160 single-ended or 80 dierenal user-dened signals

• 24 transceiver dierenal pairs

• 6 transceiver dierenal clocks

• 4 dierenal clocks

• 239 ground and 19 power connecons

Chapter 3: Board Component Descriptions

UG1410 (v1.0) July 8, 2020 www.xilinx.com

ZCU208 Board User Guide 56

Loading...

Loading...