MC96F6432

108 June 22, 2018 Ver. 2.9

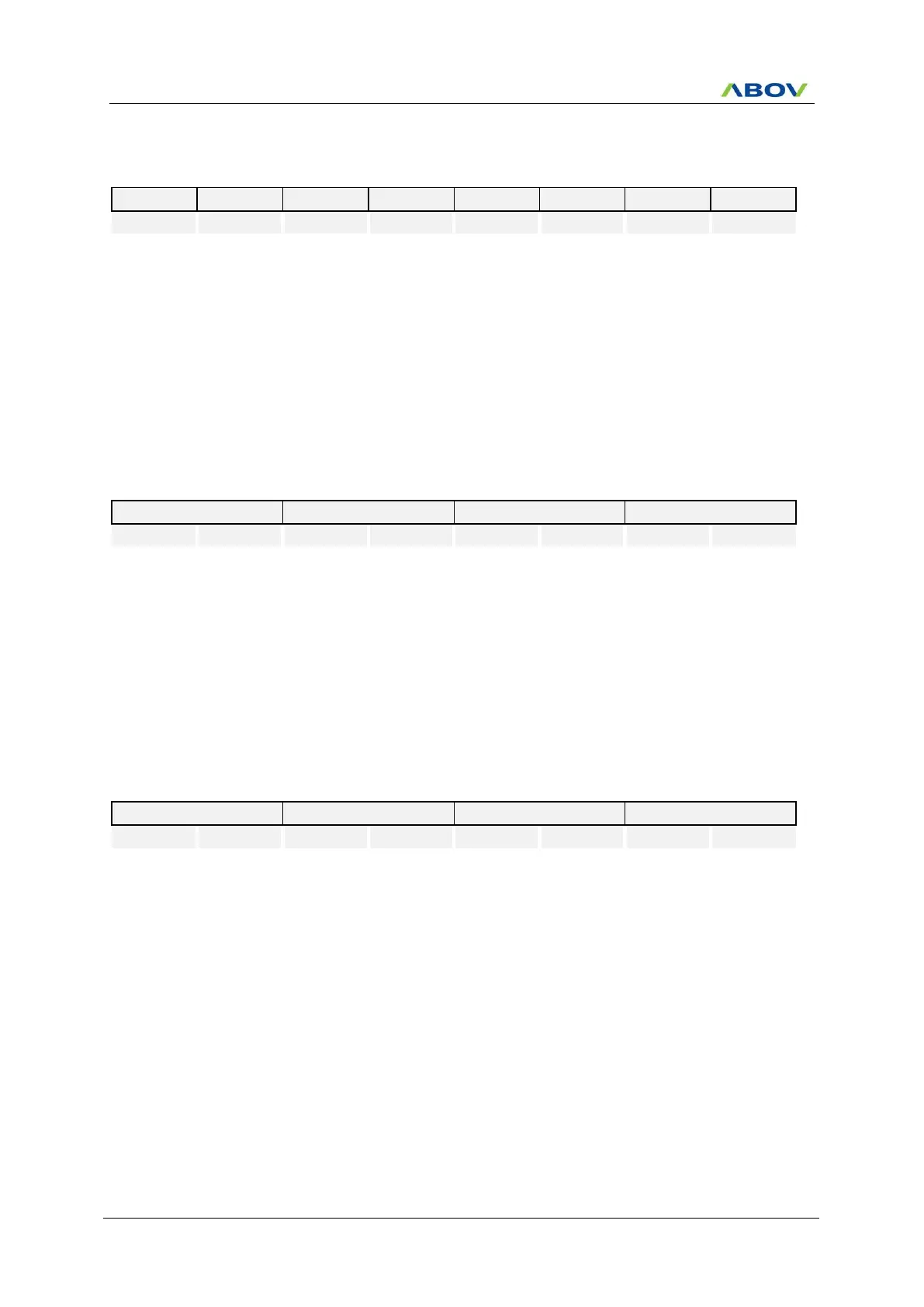

EIFLAG0 (External Interrupt Flag 0 Register) : C0H

Initial value : 00H

When an External Interrupt 0-7 is occurred, the flag becomes ‘1’.

The flag is cleared only by writing ‘0’ to the bit. So, the flag should

be cleared by software. Writing “1” has no effect.

External Interrupt 0 ~ 7 not occurred

External Interrupt 0 ~ 7 occurred

Note) Do not use the “direct bit test and branch” instruction for input port, more detail information is at

Appendix B.

Example) Avoid direct input port bit test and branch condition as below

If(FLAG0) → if(EIFLAG0 & 0x01)

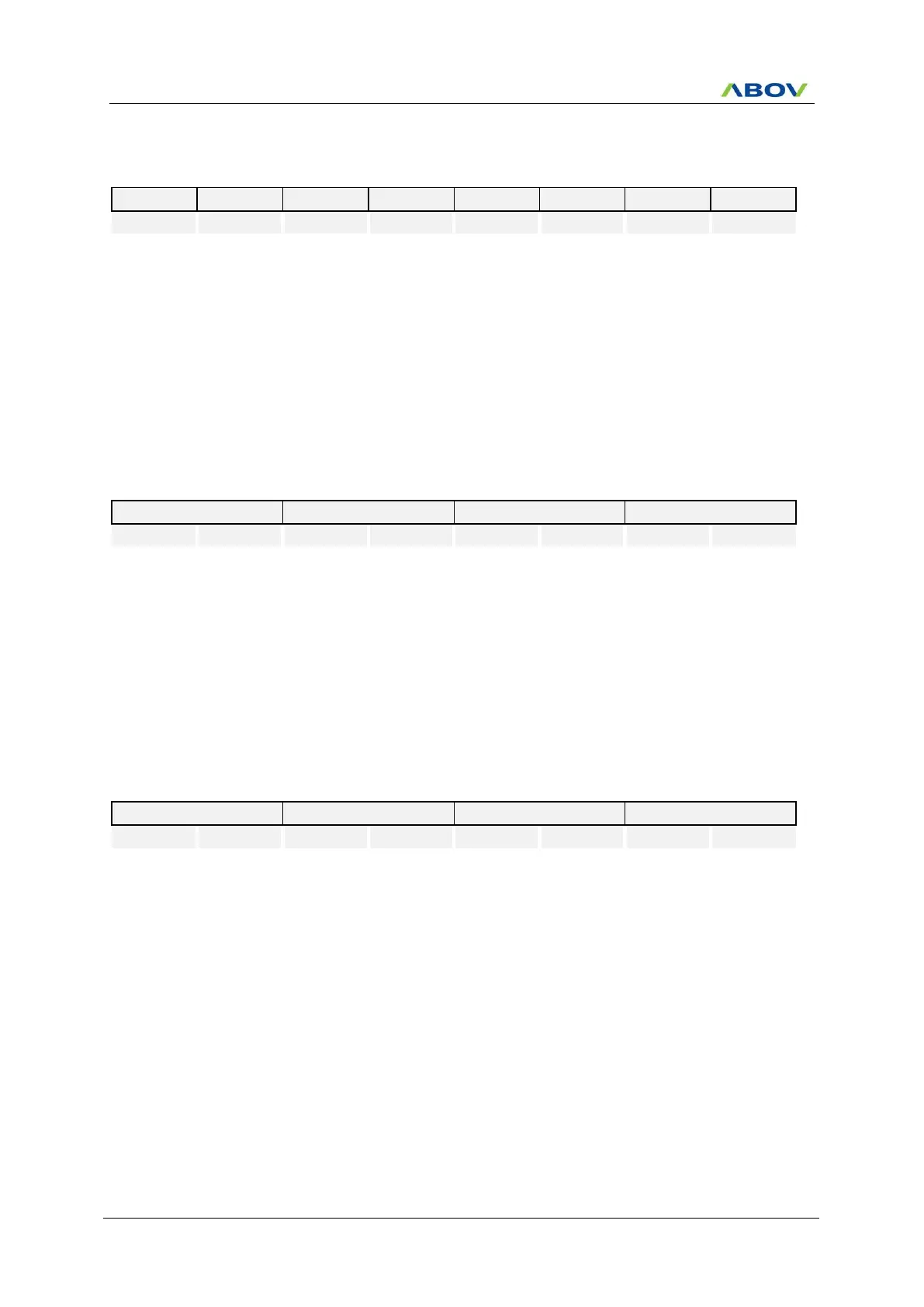

EIPOL0H (External Interrupt Polarity 0 High Register): A5H

Initial value: 00H

External interrupt (EINT7, EINT6, EINT5, EINT4) polarity selection

Interrupt on falling edge

Interrupt on both of rising and falling edge

EIPOL0L (External Interrupt Polarity 0 Low Register): A4H

Initial value: 00H

External interrupt (EINT0, EINT1, EINT2, EINT3) polarity selection

Interrupt on falling edge

Interrupt on both of rising and falling edge

Loading...

Loading...