MC96F6432

June 22, 2018 Ver. 2.9 205

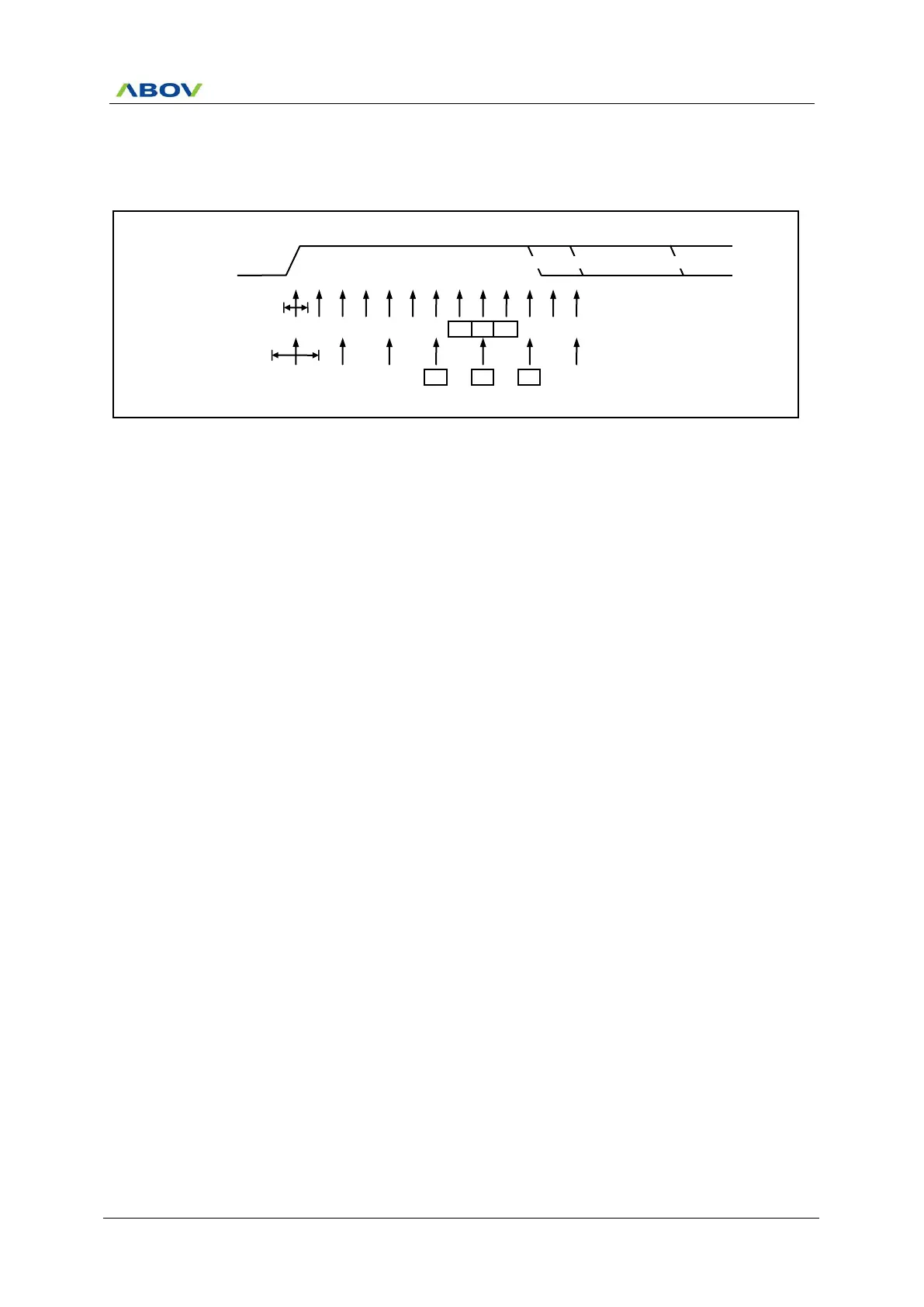

The process for detecting stop bit is like clock and data recovery process. That is, if 2 or more samples of 3

center values have high level, correct stop bit is detected, else a frame error (FE0) flag is set. After deciding

whether the first stop bit is valid or not, the Receiver goes to idle state and monitors the RXD0 line to check a

valid high to low transition is detected (start bit detection).

Figure 11.63 Stop Bit Sampling and Next Start Bit Sampling (USI0)

Loading...

Loading...