MC96F6432

June 22, 2018 Ver. 2.9 193

11.11.7 Register Description for ADC

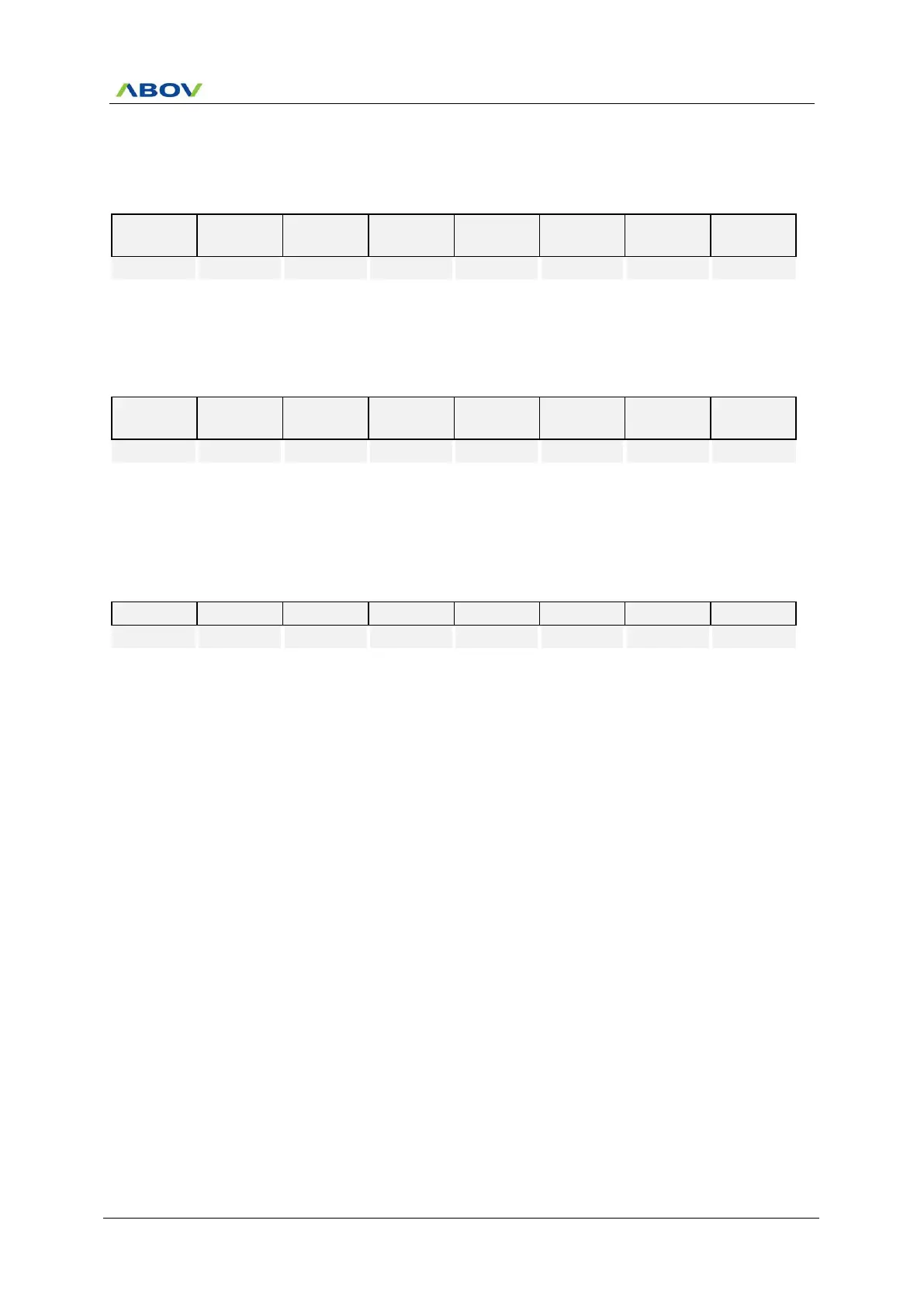

ADCDRH (A/D Converter Data High Register) : 9FH

Initial value : xxH

MSB align, A/D Converter High Data (8-bit)

LSB align, A/D Converter High Data (4-bit)

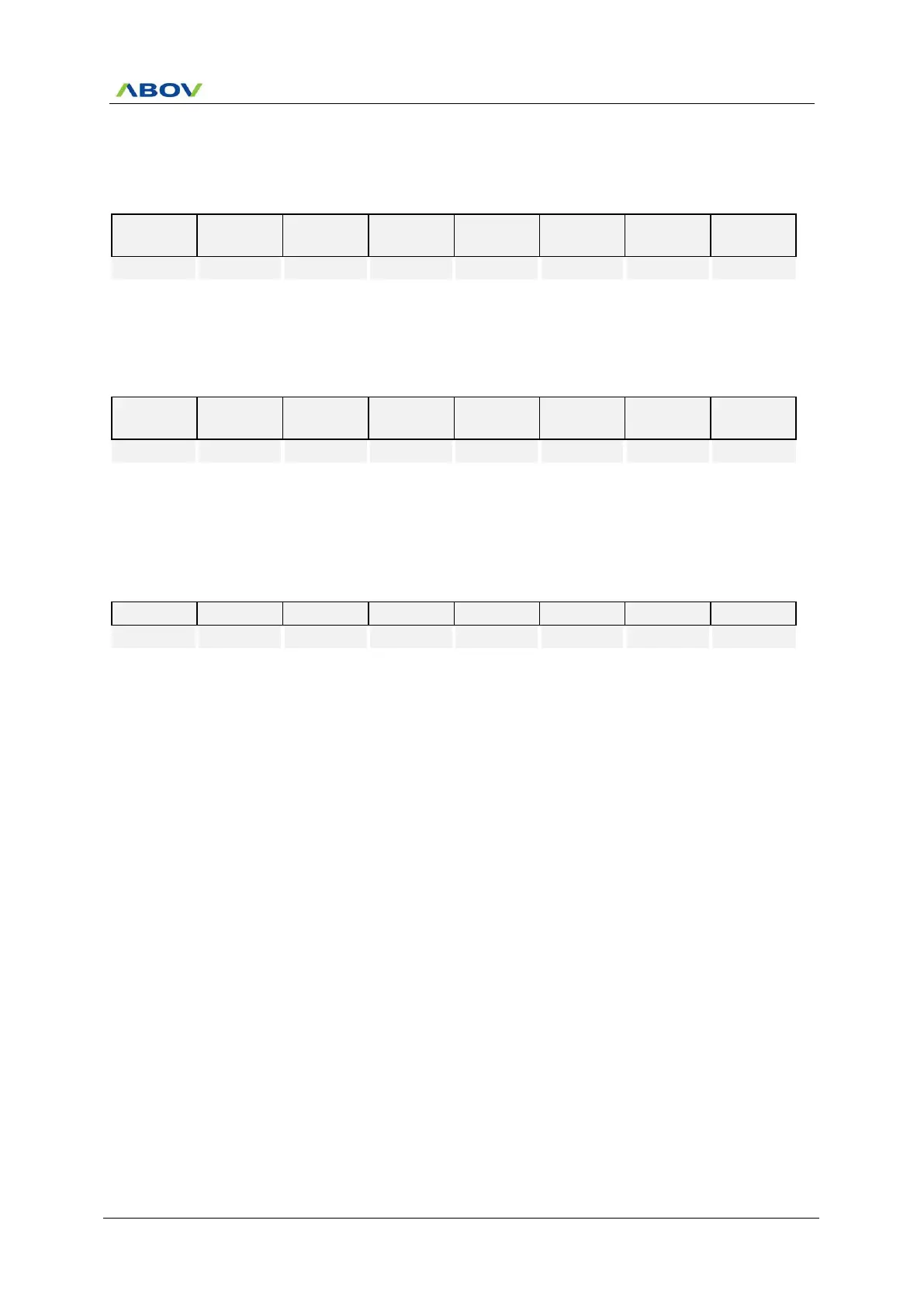

ADCDRL (A/D Converter Data Low Register) : 9EH

Initial value : xxH

MSB align, A/D Converter Low Data (4-bit)

LSB align, A/D Converter Low Data (8-bit)

ADCCRH (A/D Converter Control High Register) : 9DH

Initial value : 00H

When ADC interrupt occurs, this bit becomes ‘1’. For clearing bit,

write ‘0’ to this bit or auto clear by INT_ACK signal. Writing “1” has

no effect.

ADC Interrupt no generation

A/D Trigger Signal Selection

Timer 4 overflow event signal

Timer 4 A match event signal

Timer 4 B match event signal

Timer 4 C match event signal

A/D Converter data align selection.

MSB align (ADCDRH[7:0], ADCDRL[7:4])

LSB align (ADCRDH[3:0], ADCDRL[7:0])

A/D Converter Clock selection

Loading...

Loading...