Rockwell Automation Publication 1444-UM001D-EN-P - June 2018 521

CIP Objects Appendix A

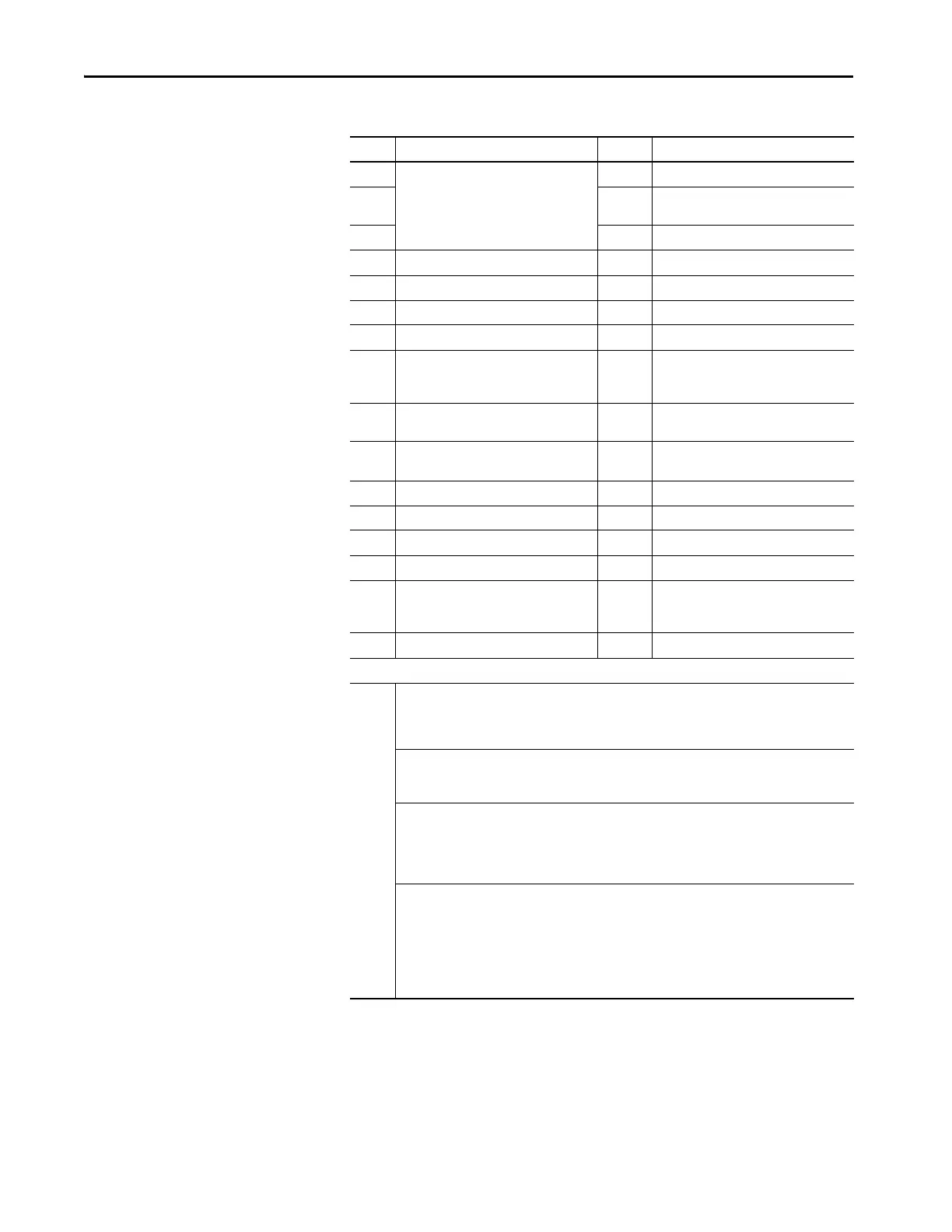

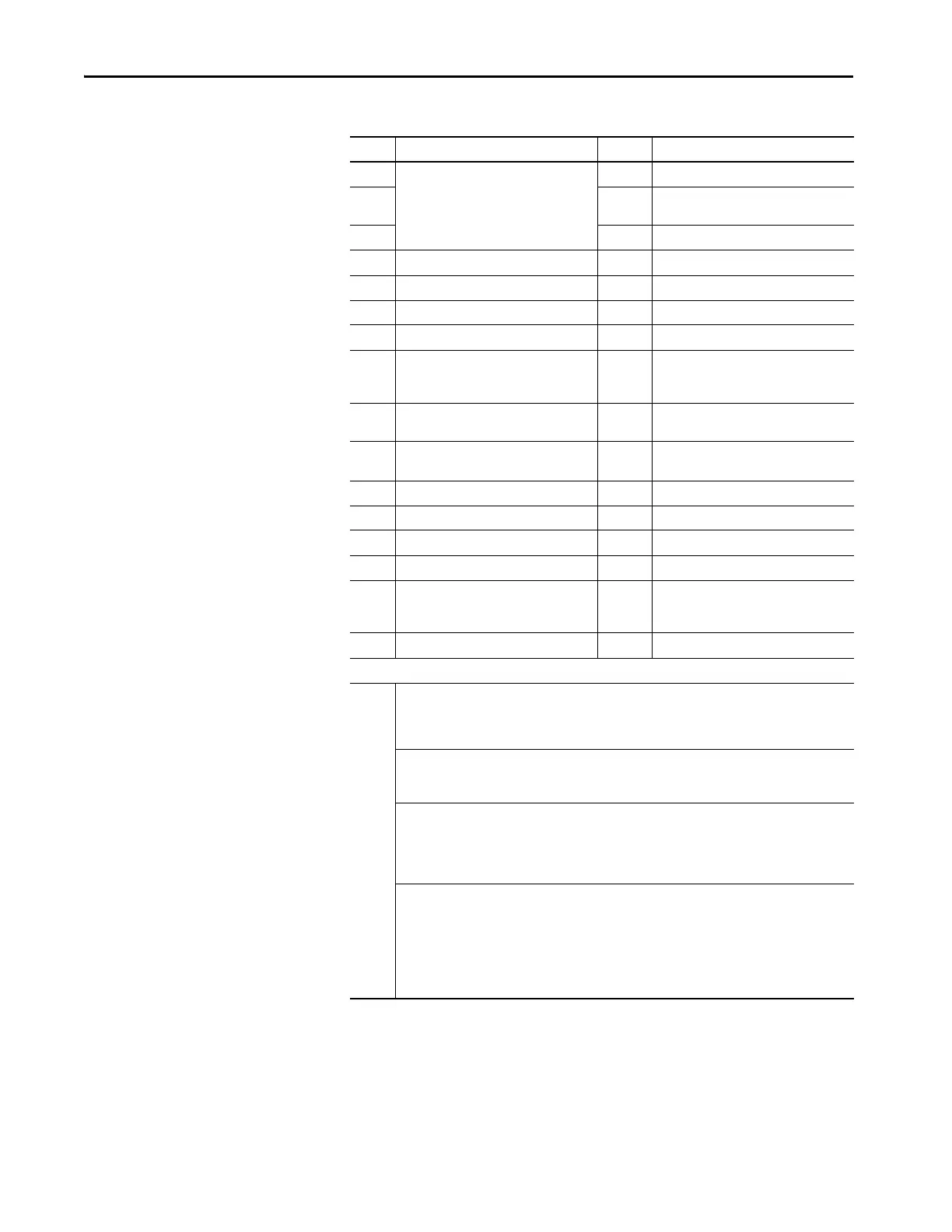

Table 275 - DSP Processor Status

Bit Description Bit Description

0 If bits 0, 1 and 2 are 0, the DSP is ready.

Anything else, the DSP is either starting up

or changing configuration.

16 A calibration time-out.

1 17 Main module relay inhibit is active (repeat of

bit 1 Alarm 0 status).

2 18 Main module relay drive test fail.

3 Spare 19 Extended loop time warning (>47 ms).

4DSP memory fault. 20 Multiplexing mode is active.

5 DSP FLASH/RAM CRC discrepancy. 21 Spare

6 Spare 22 Any speed fail.

7 DSP Reset/Power cycle indication – set

when the DSP is running from a DSP Flash

configuration.

23 Set if current speed > 1x the maximum

speed for synchronous measurements.

8 High temperature warning. 24 Set if current speed > 2x the maximum

speed for synchronous measurements.

9 Any SPM active. 25 Set if current speed < the minimum speed

for synchronous sampling.

10 DSP New Configuration. 26 Extended loop time warning (>100 ms).

11 Spare 27 Summary Fault for main module.

12 Any alarm inhibit active. 28 Summary Fault for expansion modules.

13 Spare 29 +5VA Power Supply Fault.

14 Any expansion bus or module fault (any

expansion module not present/responding

or a configuration error).

30 +24V Power Supply Fault.

15 Any calibration error. 31 -24V Power Supply Fault.

Notes

Bit 5: If on recalling a configuration from flash the DSP finds a CRC mismatch, the configuration is

considered corrupt. In this case the module sets bit 5 and load an internal default configuration from

firmware. This presents a corrupt configuration from disrupting the ability to reload the required

configuration from the DSP.

Bit 7: Is briefly set during the start-up sequence but at other times may indicate the DSP has reset or that

configuration by the auxiliary processor has failed (user should initiate another download action to make

sure the module is correctly configured and to clear this indication).

Bit 10: Set when the DSP receives a different configuration, unset at power-up or when it receives the

same configuration gain. As the auxiliary processor helps prevent internal configuration when there are

no changes. DSP receives the same data again when only configuration data has changed or irrespective

of any change, if DSP or an expansion module is in fault status. So when there is a DSP configuration

change, this bit usually stays set until the next power cycle or module reset.

Bits 23-25: Full bandwidth synchronous sampling is available while the speed is between the minimum

and maximum RPM. Between the maximum RPM and 2x the maximum RPM synchronous sampling is

usable but has reduced bandwidth.

Speeds lower than the minimum or >2x the maximum RPM are outside the operating envelope for

synchronous sampling.

NOTE: These are common to any channel/tacho, and therefore it is possible for bits 23/24 to be set at the

same time as bit 25.

Loading...

Loading...