0.6 (2019–07–25)

Amlogic Proprietary and Confidential

Copyright © Amlogic. All rights reserved.

34

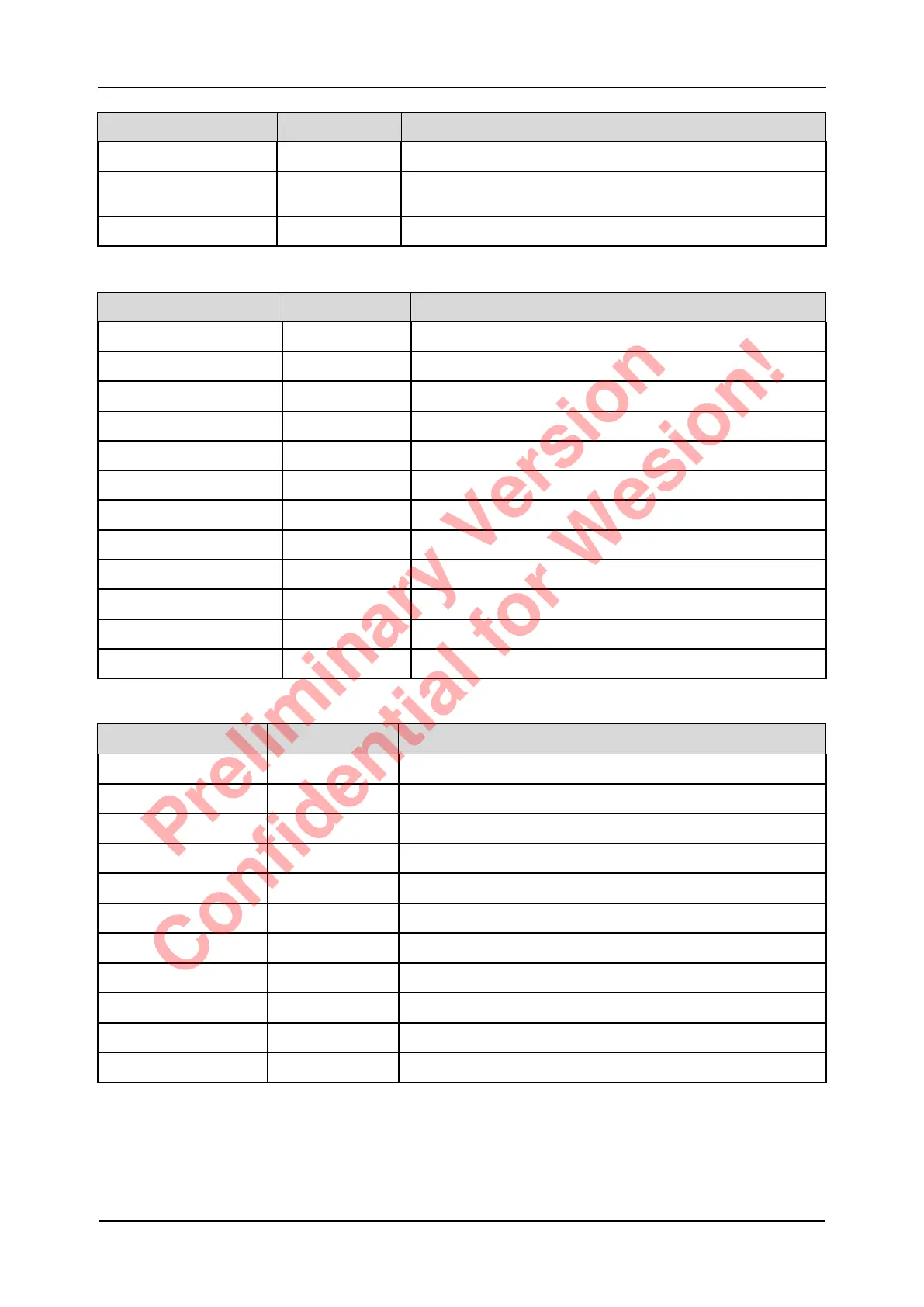

Signal Name Type Description

PWMAO_B DO PWM B output signal in Always On domain

PWMAO_C / PWMAO_C_

HIZ

DO PWM C output signal in Always On domain, or extended HiZ

function of PWMAO_C

PWMAO_D DO PWM D output signal in Always On domain

Table 4-18 I2C Interface Signal Description

Signal Name Type Description

I2C_AO_ M0_ SCL DO I2C bus port 0 clock output, Master mode, in AO domain

I2C_AO _M0_SDA DIO I2C bus port 0 data input/output, Master mode, in AO domain

I2C_AO_S0_SCL DI I2C bus port 0 clock input, Slave mode, in AO domain

I2C_AO_S0_SDA DIO I2C bus port 0 data input/output, Slave mode, in AO domain

I2C_EE_M0_SCL DO I2C bus port 0 clock output, Master mode, in EE domain

I2C_EE _M0_SDA DIO I2C bus port 0 data input/output, Master mode, in EE domain

I2C_EE_M1_SCL DO I2C bus port 1 clock output, Master mode, in EE domain

I2C_EE _M1_SDA DIO I2C bus port 1 data input/output, Master mode, in EE domain

I2C_EE_M2_SCL DO I2C bus port 2 clock output, Master mode, in EE domain

I2C_EE _M2_SDA DIO I2C bus port 2 data input/output, Master mode, in EE domain

I2C_EE_M3_SCL DO I2C bus port 3 clock output, Master mode, in EE domain

I2C_EE_M3_SDA DIO I2C bus port 3 data input/output, Master mode, in EE domain

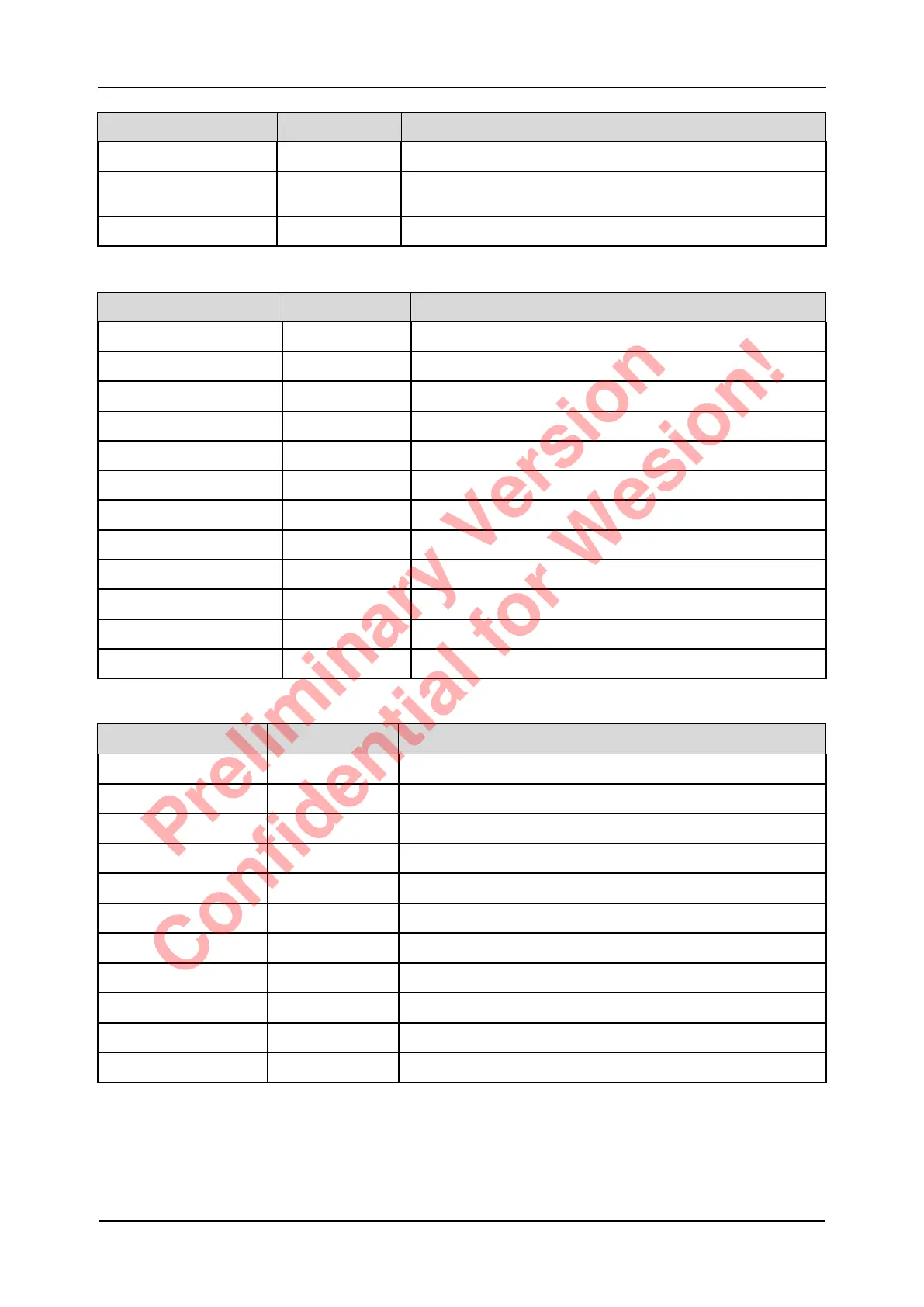

Table 4-19 eMMC Interface Signal Description

Signal Name Type Description

EMMC_D0 DIO eMMC/NAND data bus bit 0 signal

EMMC_D1 DIO eMMC/NAND data bus bit 1 signal

EMMC_D2 DIO eMMC/NAND data bus bit 2 signal

EMMC_D3 DIO eMMC/NAND data bus bit 3 signal

EMMC_D4 DIO eMMC/NAND data bus bit 4 signal

EMMC_D5 DIO eMMC/NAND data bus bit 5 signal

EMMC_D6 DIO eMMC/NAND data bus bit 6 signal

EMMC_D7 DIO eMMC/NAND data bus bit 7 signal

EMMC_CLK DO eMMC clock signal

EMMC_CMD DIO eMMC command signal

EMMC_NAND_DQS DIO eMMC/NAND data strobe

S905D3 Quick Reference Manual 4 Pinout Specification

Preliminary Version

Confidential for Wesion!

Loading...

Loading...