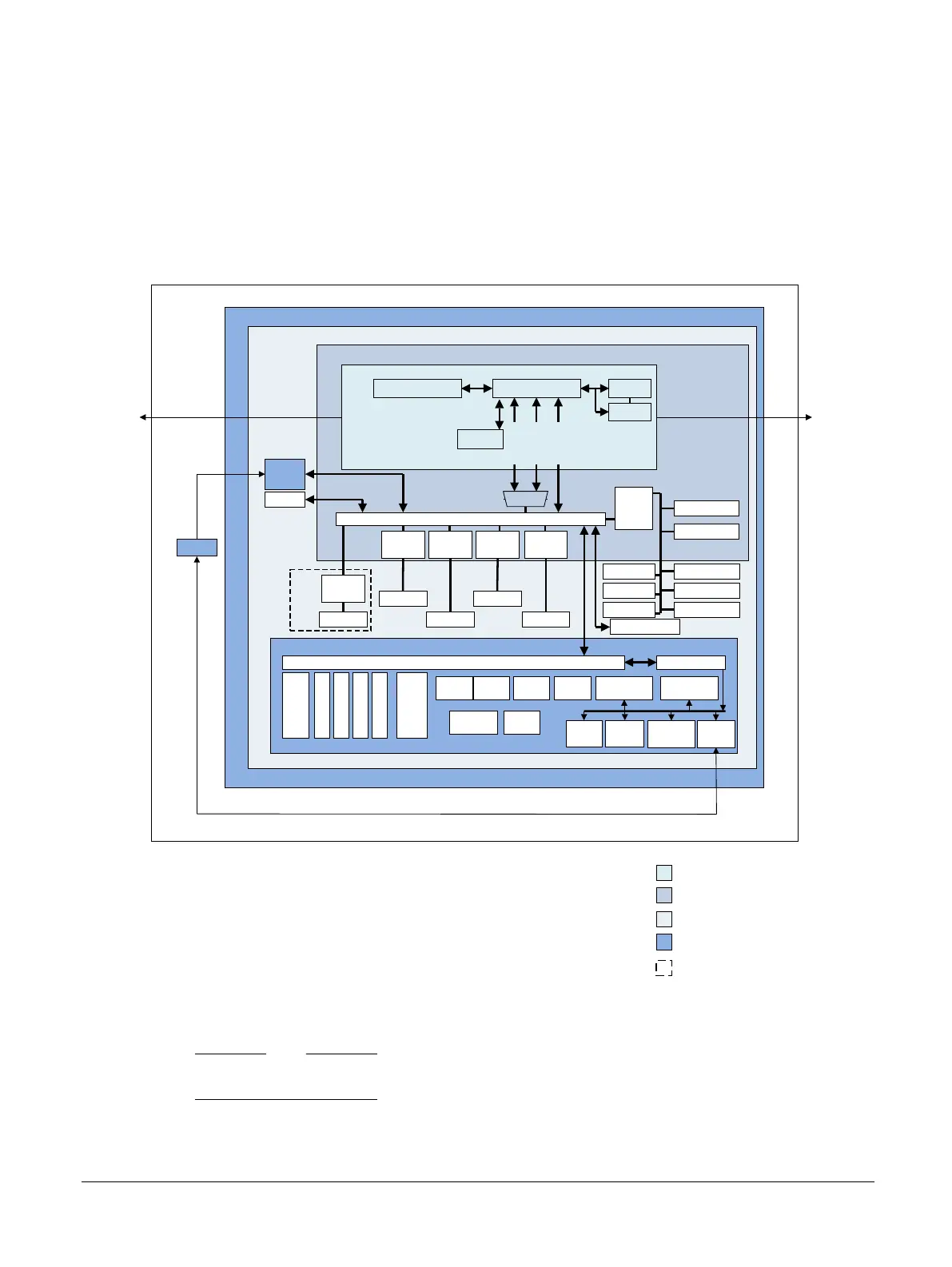

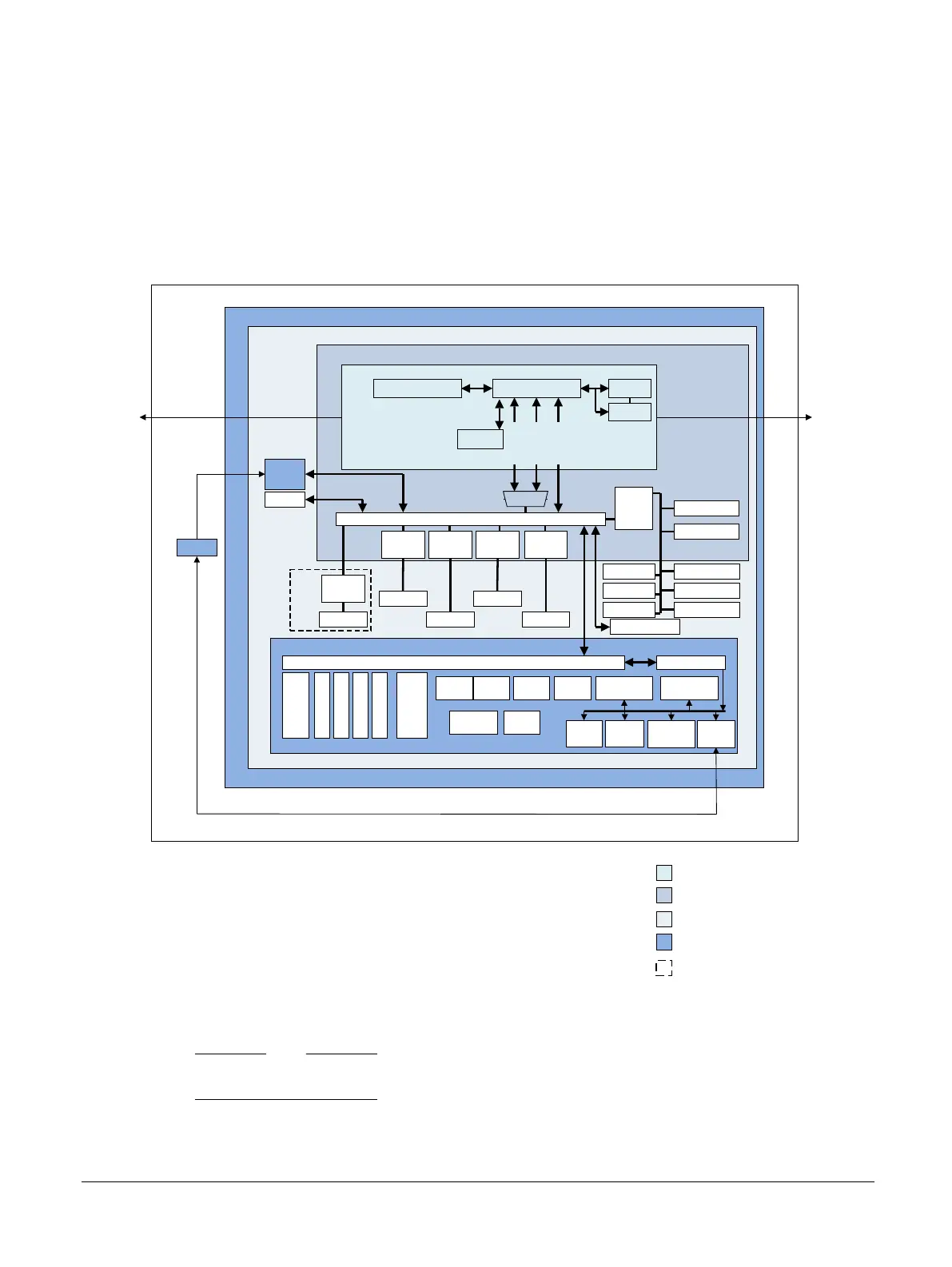

3.1 System overview

The Soft Macro Model (SMM) is an FPGA implementation of an ARM processor or subsystem. The

SMM is based on the SSE-050 Subsystem. Extra peripherals that are required by the FPGA are placed on

the expansion of APB and AHB ports.

The following figure shows the block diagram of the FPGA design, indicating the Cortex-M3 processor

from DesignStart, the CMSDK components (peripherals and interconnect), and the interfaces to the

MPS2+ platform peripherals.

FPGA

User Domain

FPGA Peripherals

flash

AHB Mux AHB to APB

IoT Subsystem

AHB

to

APB

Timer

AHB Mux

SRAM1

SRAM0

SRAM3

SRAM2

SRAMF

SPI

MCC

GPIO

GPIO

GPIO

GPIO

Spare

Spare

AHB to

SRAM

AHB to

SRAM

AHB to

SRAM

AHB to

SRAM

AHB to

SRAM

System

Controler

Ethernet VGA

FPGA I/O Audio I

2

S

SPI x2

SBCon

x2

SCC

Spare AHB

Arduino

Peripherals

ZBT ZBT ZBT ZBT

Cortex-M3

Cortex-M3

TPIU

DAP ETM

Timer

TRNG

RTC

Cortex-M3 as obfuscated RTL

IoT subsystem

WIC

I-Code

D-Code

System

User domain

FPGA level

MPS2+ FPGA platform

UART x2

Watchdog

Dual Timer

UART

x3

Debug

Trace

Flash subsystem modeled

using SRAM

Figure 3-1 System overview

Note

This block diagram shows the functional hierarchy of the FPGA design.

3 FPGA platform overview

3.1 System overview

ARM 100896_0000_00_en Copyright © 2017 ARM Limited or its affiliates. All rights reserved. 3-25

Non-Confidential

Loading...

Loading...