3.4 External Zero Bus Turnaround SSRAM

This section describes the Zero Bus Turnaround (ZBT) SSRAM in the FPGA platform.

This section contains the following subsections:

• 3.4.1 ZBT SSRAM1 on page 3-28.

• 3.4.2 ZBT SSRAM2 and ZBT SSRAM3 on page 3-28.

3.4.1 ZBT SSRAM1

This section describes the Zero Bus Turnaround (ZBT) SSRAM in the code region, which is an

additional area in memory which can be used to store executable code.

This interface consists of two external 32-bit ZBT SSRAMs in parallel, forming a 64-bit ZBT SSRAM.

This makes 4MB available (each ZBT SSRAM is 2MB).

This ZBT SSRAM1 is connected through the AHB.

3.4.2 ZBT SSRAM2 and ZBT SSRAM3

ZBT SSRAM2 and ZBT SSRAM3 are two external 32-bit ZBT SSRAMs that are connected to two

independent ZBT interfaces.

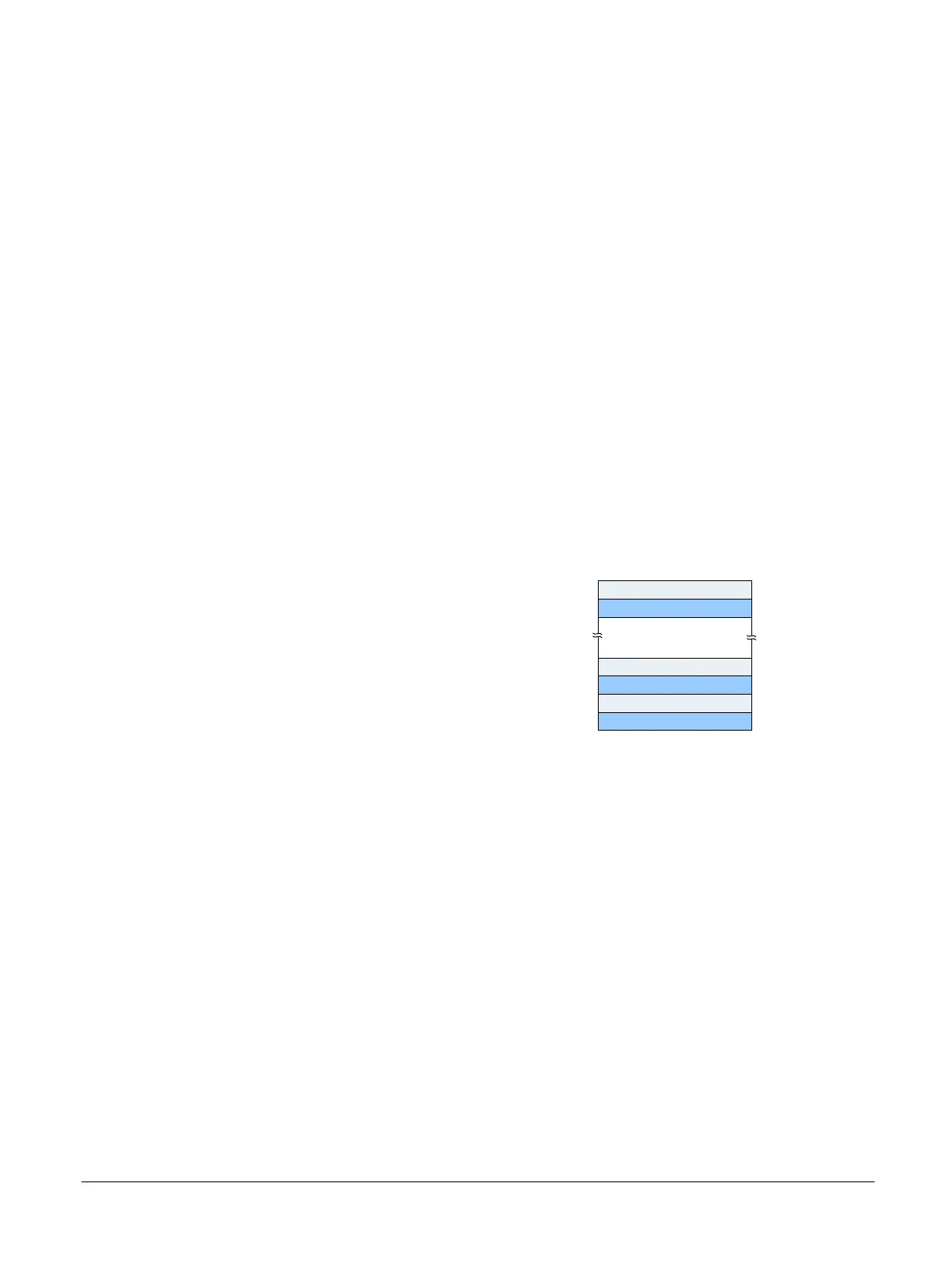

Each ZBT SSRAM occupies 2MB of memory space. When combined, the ZBT SSRAMs occupy 4MB

of memory space. This provides an additional RAM region. The addresses of the two ZBT SSRAMs are

interleaved as shown in the following diagram:

ZBT SSRAM2

ZBT SSRAM3

ZBT SSRAM3/

ZBT SSRAM2

ZBT SSRAM2

ZBT SSRAM3

0x2040_0008

0x2040_000C

0x207F_FFF8

0x207F_FFFC

ZBT SSRAM2

ZBT SSRAM3

0x2040_0000

0x2040_0004

Figure 3-2 32-bit ZBT SSRAM memory space

The ZBT SSRAM2 and ZBT SSRAM3 are connected through the AHB.

3 FPGA platform overview

3.4 External Zero Bus Turnaround SSRAM

ARM 100896_0000_00_en Copyright © 2017 ARM Limited or its affiliates. All rights reserved. 3-28

Non-Confidential

Loading...

Loading...