4.2 Derived clocks

There are several derived clocks for the FPGA design.

The following table shows the derived clocks and respective frequencies for the system:

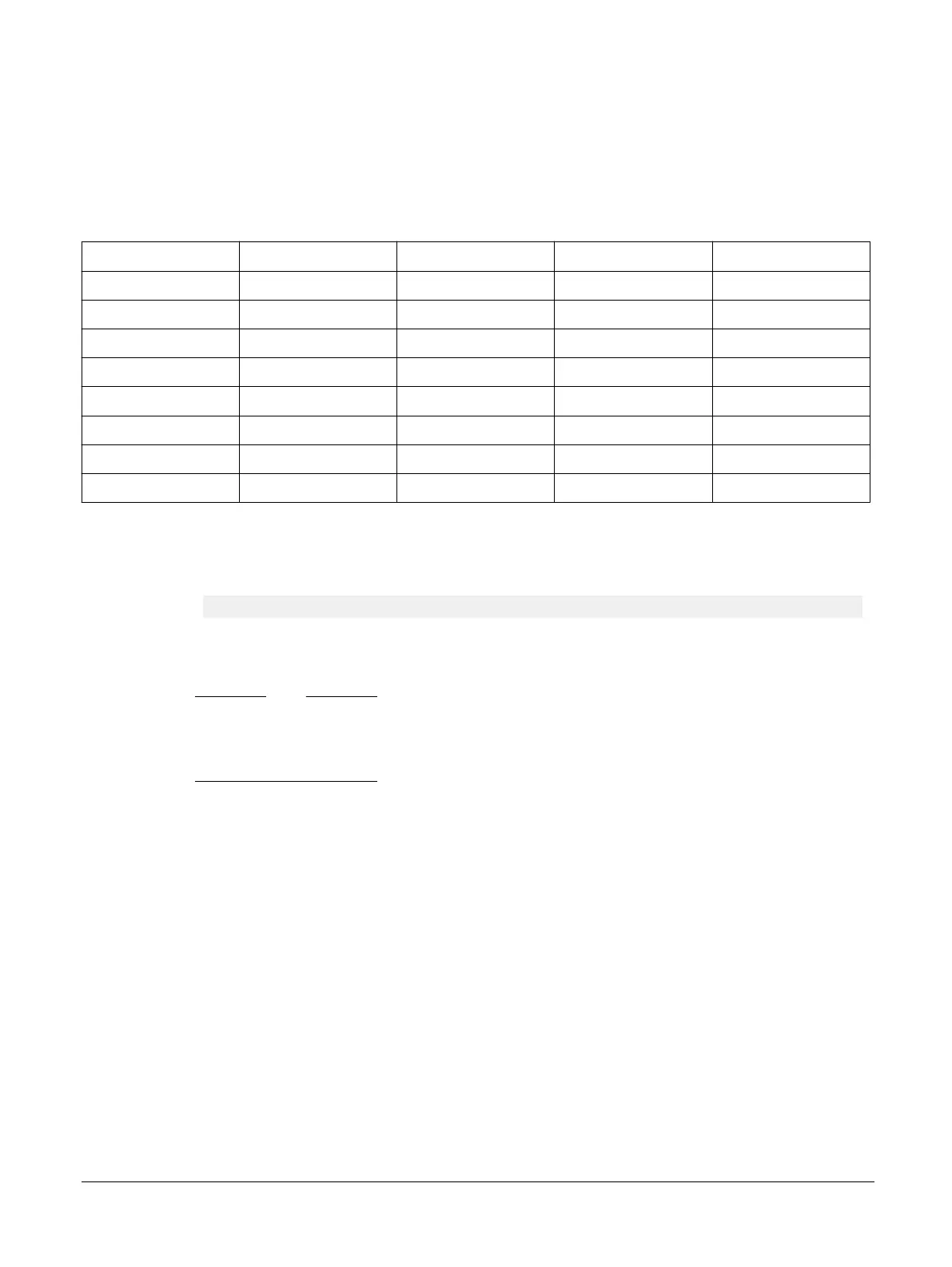

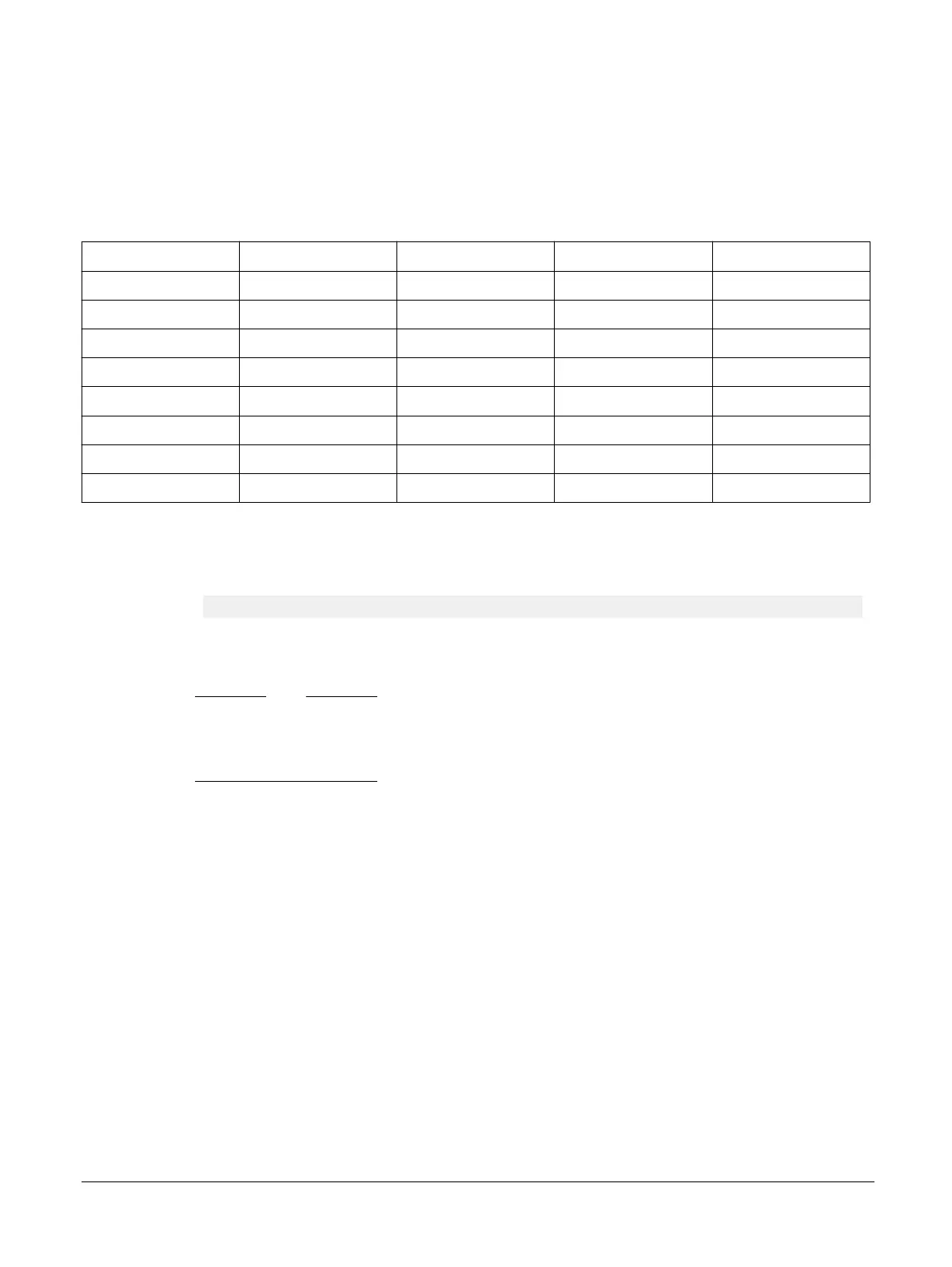

Table 4-2 Derived clocks

Name Frequency Division Factor Multiplication Factor Derived From

SYSCLK 25MHz 2 1 OSCCLK[0]

DBGCLK 25MHz 2 1 OSCCLK[0]

SPICLCD 25MHz 2 1 OSCCLK[0]

SPICON 25MHz 2 1 OSCCLK[0]

I2CCLCD 25MHz 2 1 OSCCLK[0]

I2CAUD 25MHz 2 1 OSCCLK[0]

AUDMCLK 12.29MHz 2 1 OSCCLK[1]

AUDSCLK 3.07MHz 8 1 OSCCLK[1]

The system clock is SYSCLOCK in the Table 4-2 Derived clocks on page 4-44.

The clock frequencies are controlled by the configuration file an511_v1.txt located in the following

directory:

MPS2+/MB/HBI0263C/AN511

As OSCCLK[0] controls the Cortex-M3 DesignStart Eval system clock (SYSCLK), it is possible to

increase the clock by changing the OSC0 value. This value can be set from 2MHz to 230MHz, with a

1% accuracy, subject to the constraints of FPGA timing performance.

Note

If the source clocks are changed, you must modify the AN511_SMM_CM3DS.sdc in the

<install_directory>/m3designstart/fpga/AN511_SMM_CM3DS/synthesis/ directory to reflect the

new clock frequencies.

4 Clocks

4.2 Derived clocks

ARM 100896_0000_00_en Copyright © 2017 ARM Limited or its affiliates. All rights reserved. 4-44

Non-Confidential

Loading...

Loading...