3.14 Audio I

2

S

A simple FIFO interface generates and receives I

2

S audio.

The following table describes the memory map for I

2

S audio registers:

Table 3-2 Audio I

2

S memory map

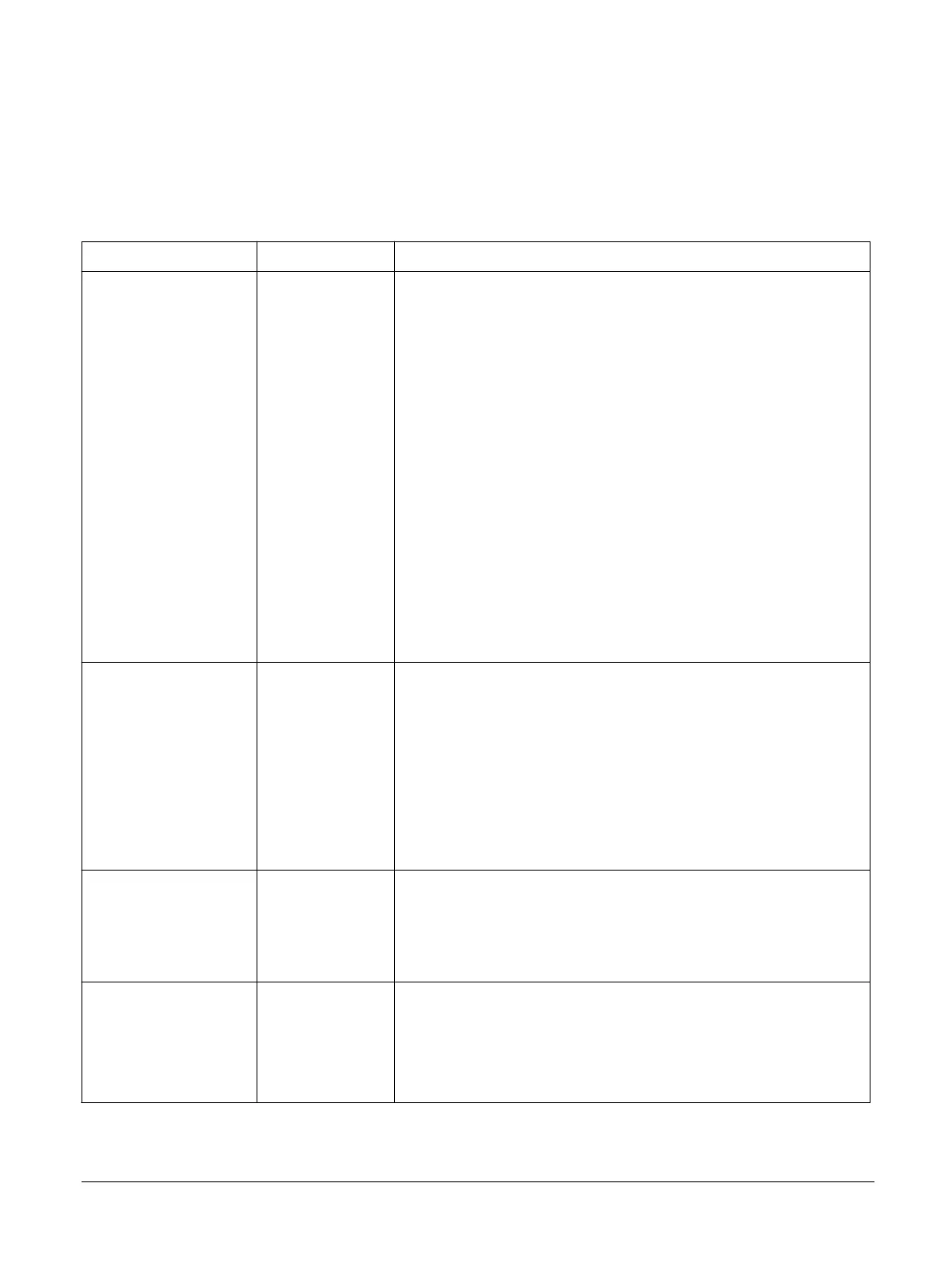

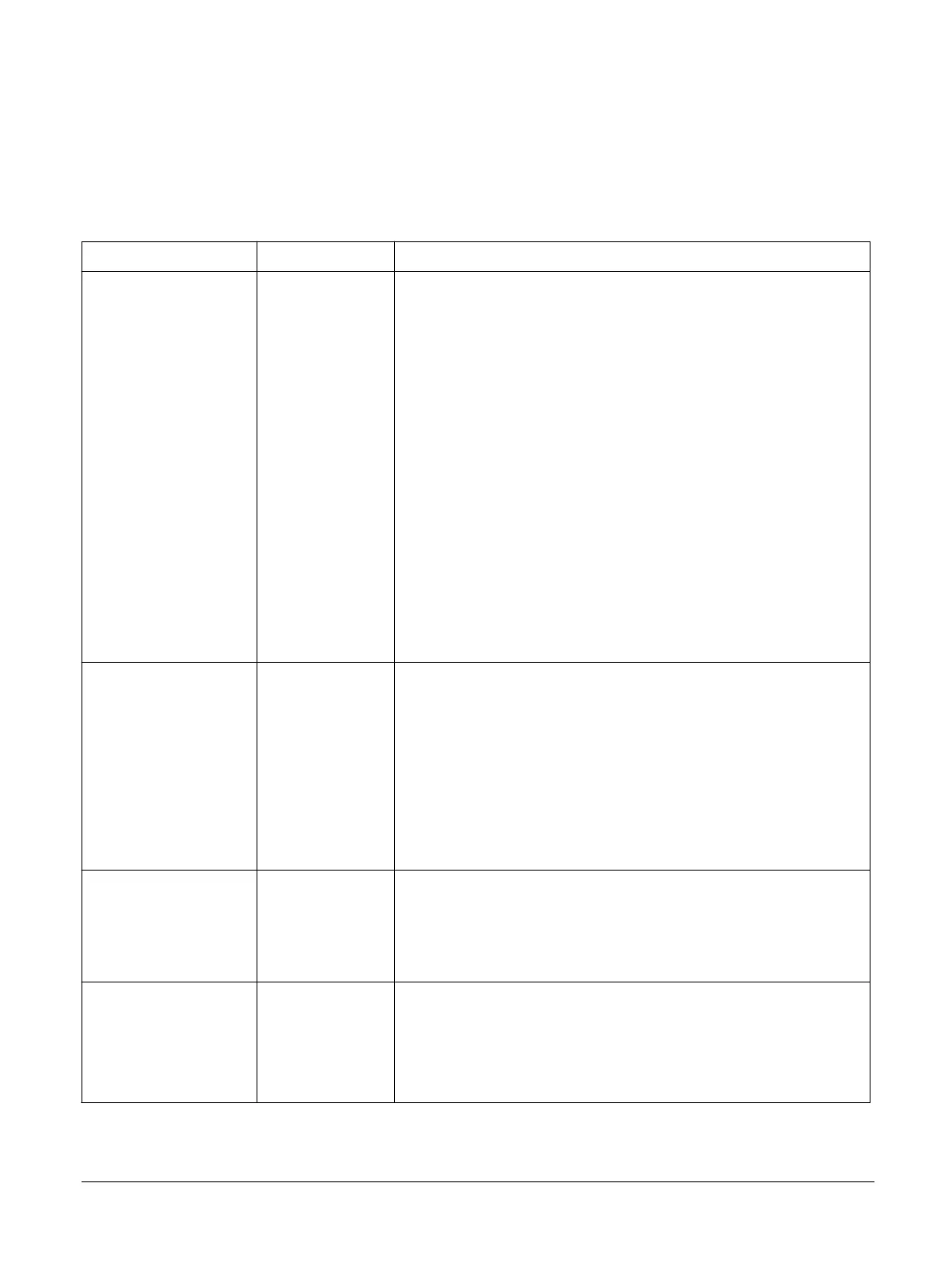

Address Name Description

0x40024000

CONTROL Control register

[31:18] Reserved

[17] Audio codec reset control (output pin)

[16] FIFO reset

[15] Reserved

[14:12] Rx Buffer IRQ Water Level - Default 2

(IRQ triggers when less than two word space is available).

[11] Reserved

[10:8] TX Buffer IRQ Water Level - Default 2

(IRQ triggers when more than two word space is available).

[7:4] Reserved

[3] Rx Interrupt Enable

[2] Rx Enable

[1] Tx Interrupt Enable

[0] Tx Enable

0x40024004

STATUS Status register

[31:6] Reserved

[5] Rx Buffer Full

[4] Rx Buffer Empty

[3] Tx Buffer Full

[2] Tx Buffer Empty

[1] Rx Buffer Alert (Depends on Water level)

[0] Tx Buffer Alert (Depends on Water level)

0x40024008

ERROR Error status register

[31:2] Reserved

[1] Rx overrun. Set this bit to clear.

[0] Tx overrun or underrun. Set this bit to clear.

0x4002400C

DIVIDE Divide ratio register (for left or right clock)

[31:10] Reserved

[9:0] LRDIV (Left/Right). The default value is 0x80.

12.288MHz / 48kHz / 2*(L+R) = 128.

3 FPGA platform overview

3.14 Audio I

2

S

ARM 100896_0000_00_en Copyright © 2017 ARM Limited or its affiliates. All rights reserved. 3-38

Non-Confidential

Loading...

Loading...