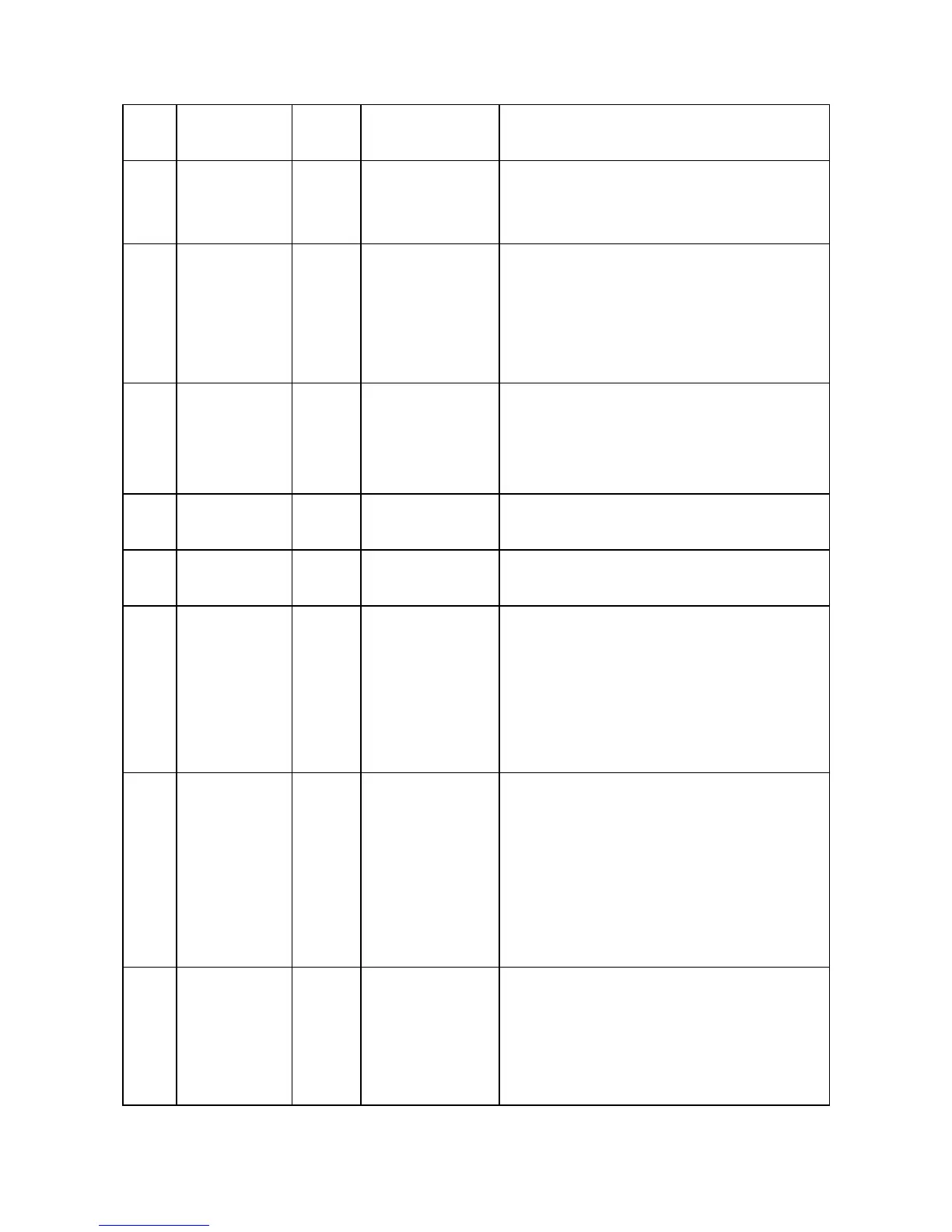

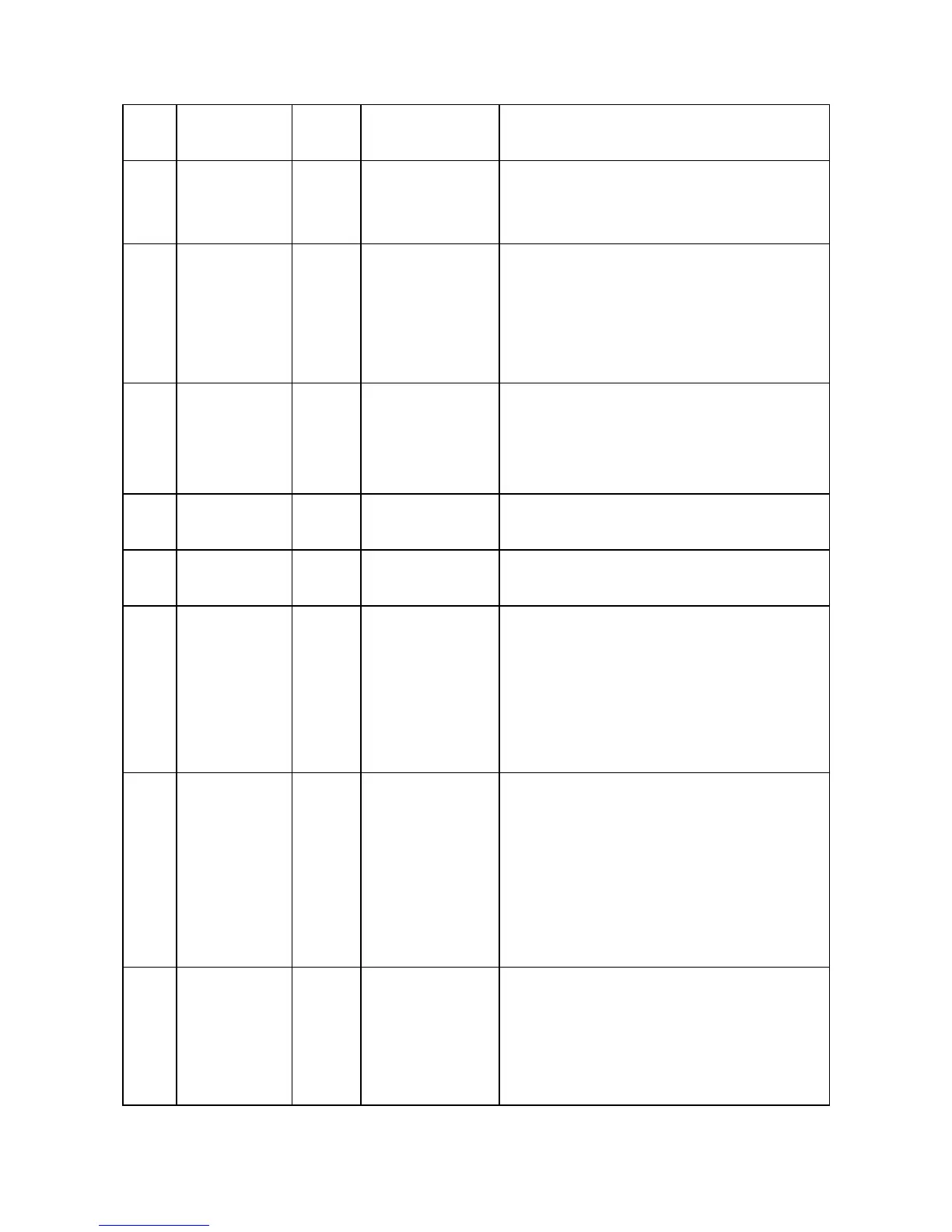

I) Serial interface port 0 data-in

II) GPIO

206 SPLRCK SDO0 Inout

1) Audio left/right channel clock of SPDIF input

2) While SPDIF input is not used:

I) Serial interface port 0 data-out II) GPIO

207 SPBCK

SDCS0

ASDATA

5

Inout

1) Audio bit clock of SPDIF input

2) While SPDIF input is not used:

I) Serial interface port 0 chip select

II) Audio serial data 5 part I : DSD data sub-woofer

Channel or Microphone output III) GPIO

209 ALRCK

InOut 4mA,

PD,SMT

1) Audio left/right channel clock

2) Trap value in power-on reset:

I) 1: use external 373

II) 0: use internal 373

210 ABCK Fs64

InOut 4mA,

SMT

1) Audio bit clock

2) Phase de-modulation

211 ACLK

InOut 4mA,

SMT

Audio DAC master clock

197 ASDATA0

InOut 4mA,

PD,SMT

1) Audio serial data 0 (Front-Left/Front-Right)

2) DSD data left channel

3) Trap value in power-on reset:

I) 1: manufactory test mode

II) 0: normal operation

4) While using external channels: ) GPO_2

202 ASDATA1

InOut 4mA,

PD,SMT

2) Audio serial data 0 (Front-Left/Front-Right)

2) DSD data right channel

3) Trap value in power-on reset:

I) 1: manufactory test mode

II) 0: normal operation

4) While using external channels:

I) GPO_2

203 ASDATA2

InOut 4mA,

PD,SMT

1) Audio serial data 1 (Left-Surround/Right-Surround)

2) DSD data left surround channel

3) Trap value in power-on reset:

I) 1: manufactory test mode

II) 0: normal operation

- 62 -

Loading...

Loading...