Commissioning

EL3773 137Version: 2.5

the frames are not arriving regularly at the EL3773. In this case the above points should be checked.

• In particular the synchronization can become more difficult if such effects occur during the start-up

phase. This may also prevent the EL3773 from entering the OP state.

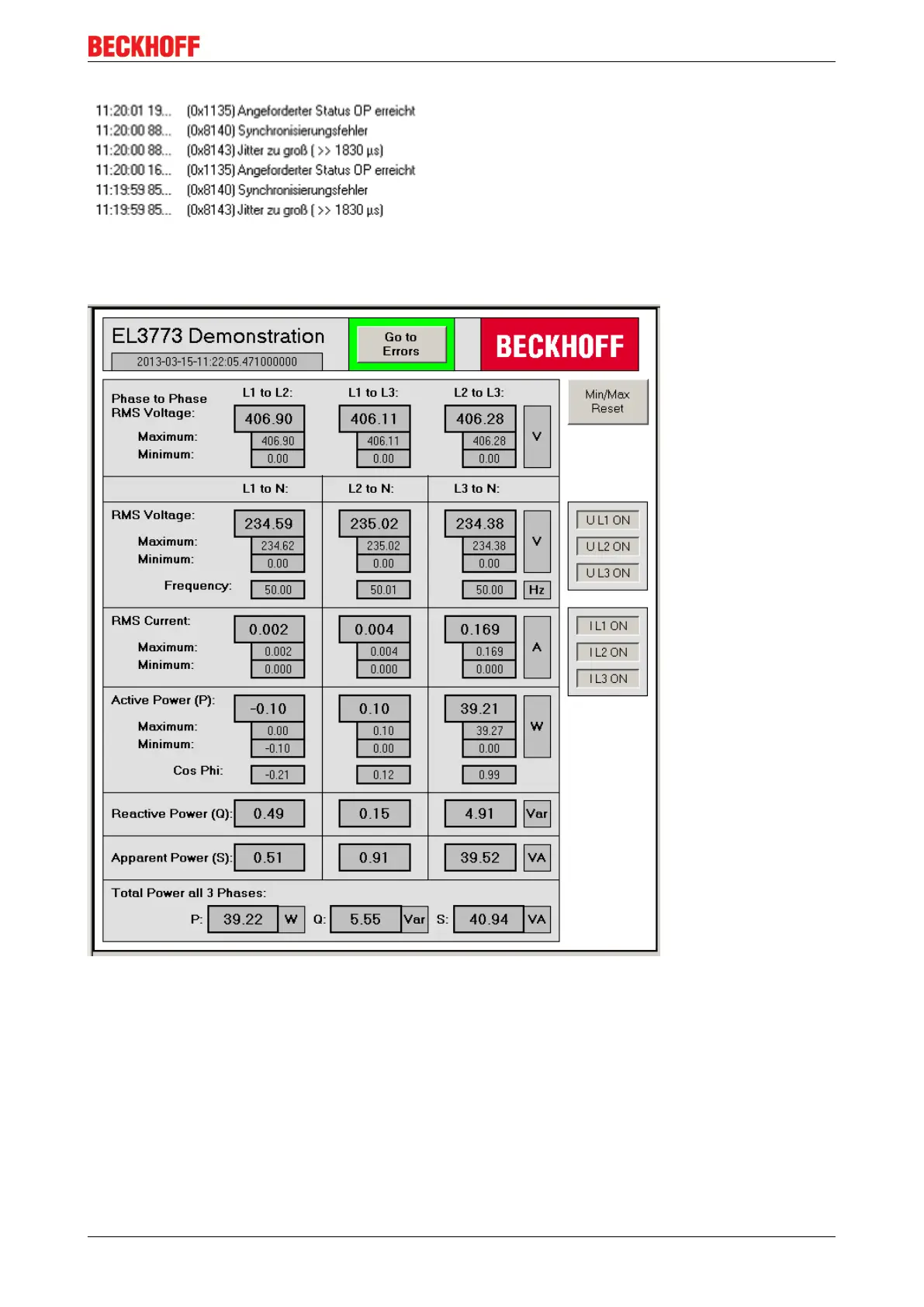

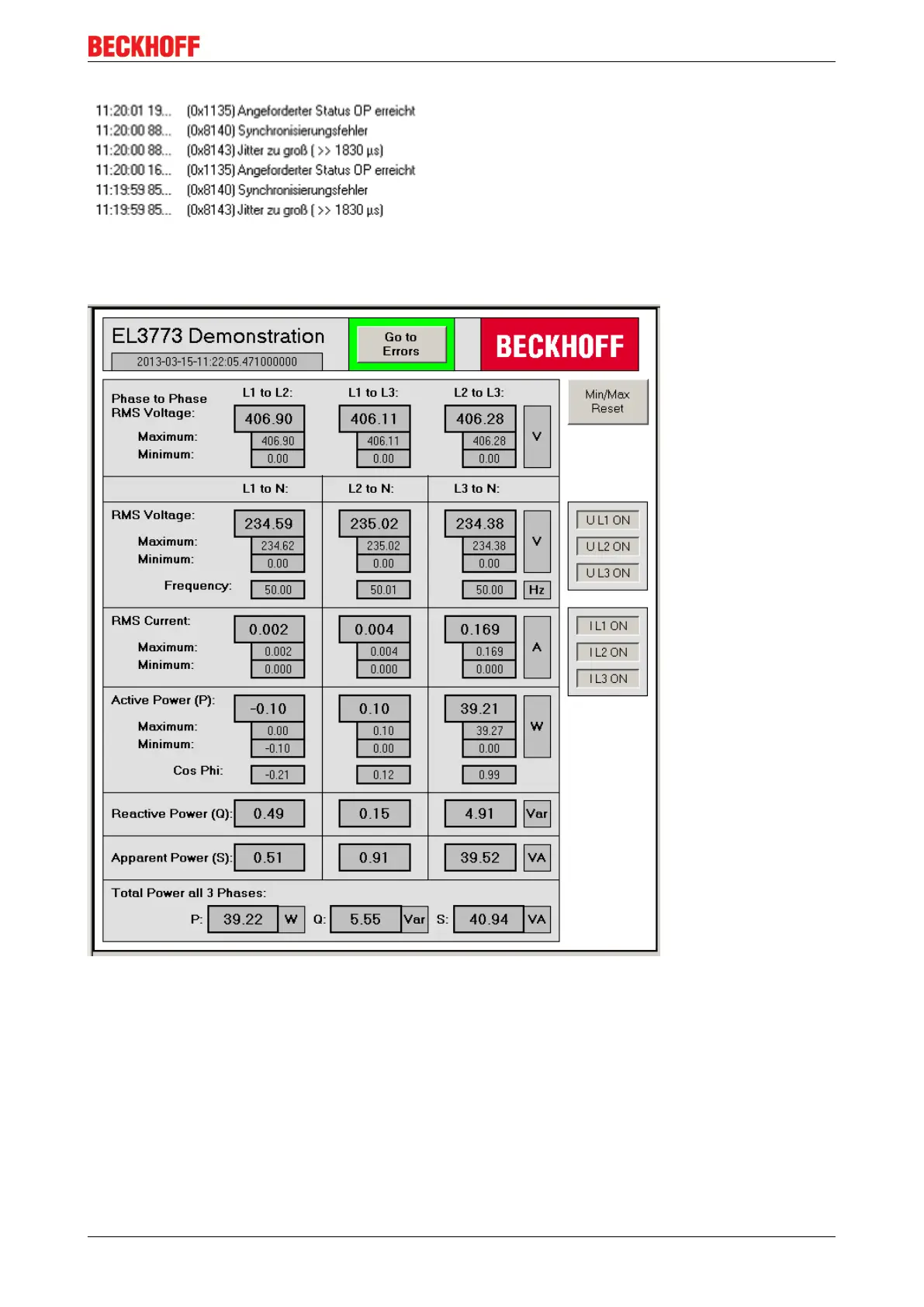

Fig.153: Visualization of example program for EL3773

In this example the input data of an EL3773 will be checked for validity and processed:

• Cycle time and oversampling freely configurable, presetting: 5ms cycle time, 20-fold oversampling

• WC, State, EtherCAT Master DevState, WcState, FrmState and status of the channels are cyclically

checked

• The data from each cycle are placed in a FIFO buffer so that, for example, the evaluation can take

place at a higher level. The size of the FIFO buffer is freely configurable

• If all data are valid, the following calculations take place:

◦ RMS voltage for each channel

◦ RMS current for each channel

Loading...

Loading...