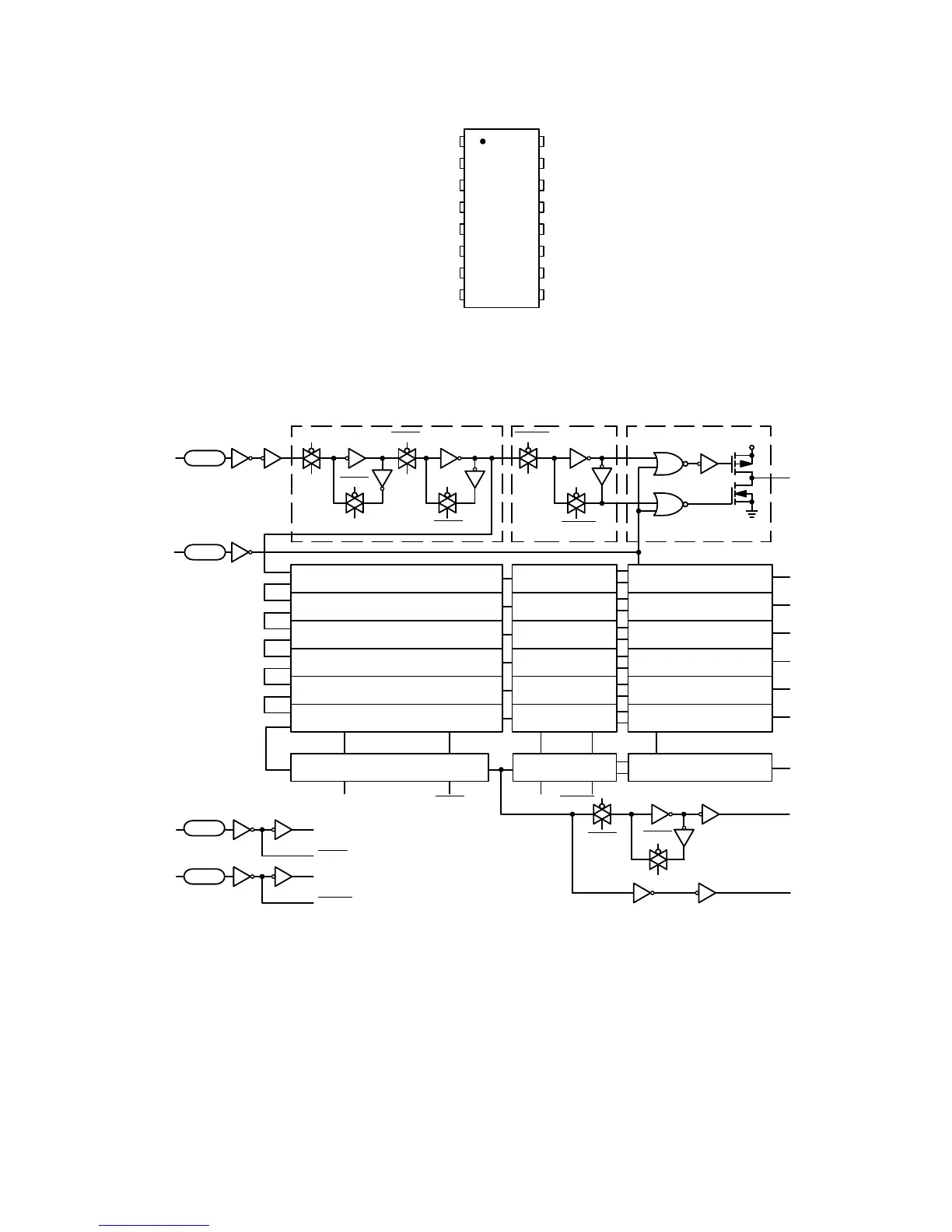

PIN ASSIGNMENT

TRUTH TABLE

Clock

Output

Enable

Strobe Data

Parallel Outputs Serial Outputs

Q1 Q

N

Q

S

* Q′

S

0 X X Z Z Q7 No Chg.

0 X X Z Z No Chg. Q7

1 0 X No Chg. No Chg. Q7 No Chg.

1 1 0 0 Q

N

−1 Q7 No Chg.

1 1 1 1 Q

N

−1 Q7 No Chg.

1 1 1 No Chg. No Chg. No Chg. Q7

Z = High Impedance X = Don’t Care

* At the positive clock edge, information in the 7th shift register stage is transferred to Q8 and Q

S

.

ORDERING INFORMATION

Device Package Shipping

†

MC14094BCPG PDIP−16

(Pb−Free)

500 Units / Rail

MC14094BDG SOIC−16

(Pb−Free)

48 Units / Rail

MC14094BDR2G

SOIC−16

(Pb−Free)

2500 Units / Tape & Reel

NLV14094BDR2G*

MC14094BDTR2G

TSSOP−16

(Pb−Free)

2500 Units / Tape & Reel

NLV14094BDTR2G*

MC14094BFELG SOEIAJ−16

(Pb−Free)

2000 Units / Tape & Reel

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging

Specifications Brochure, BRD8011/D.

*NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC−Q100 Qualified and PPAP

Capable.

Loading...

Loading...