Cinterion

®

LTE Terminals Hardware Interface Description

8.3 Complete Watchdog Configuration

101

ELSxT_HID_v04 2018-09-04

Confidential / Preliminary

Page 85 of 102

8.3.1.12 Configure ADC1_IN/DSR0/SPI_CLK Line

This command configures the the ADC/DSR0/SPI_CLK signal on the GPIO connector to be ei-

ther an analog input line (ADC) or a digital output line (DSR0/SPI_CLK). If configured as analog

input, the signal is connected to the LTE module‘s ADC1_IN line. If configured as digital output,

the signal is connected to the LTE module‘s DSR0/SPI_CLK line that can be configured to be

either DSR0 or SPI_CLK (SPI_CLK not available for BGS5T USB).

Note: If configuring the ADC1_IN/DSR0/SPI_CLK line please take great care to be in accor-

dance with the LTE module‘s current configuration of the ADC1_IN and DSR0/SPI_CLK sig-

nals.

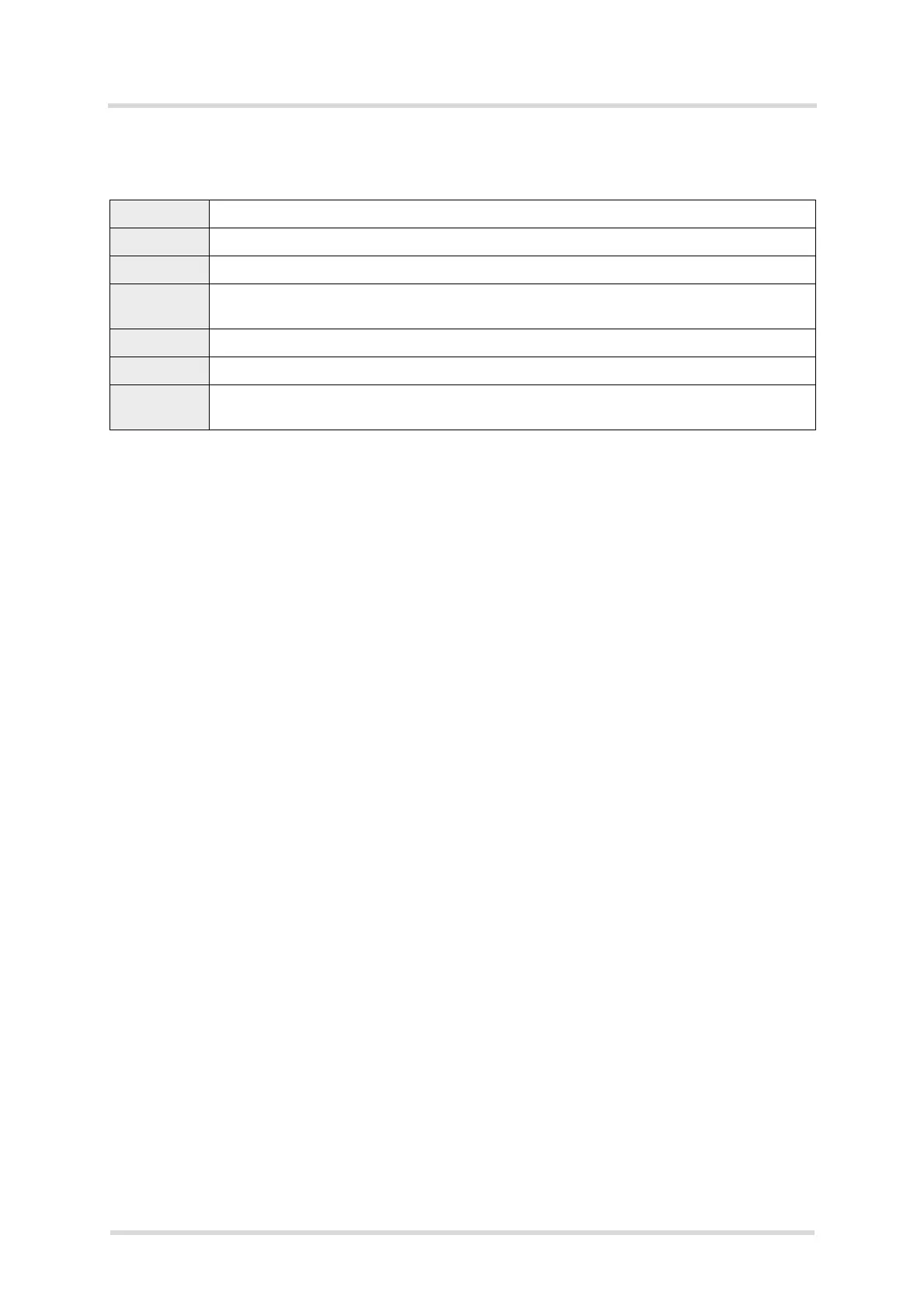

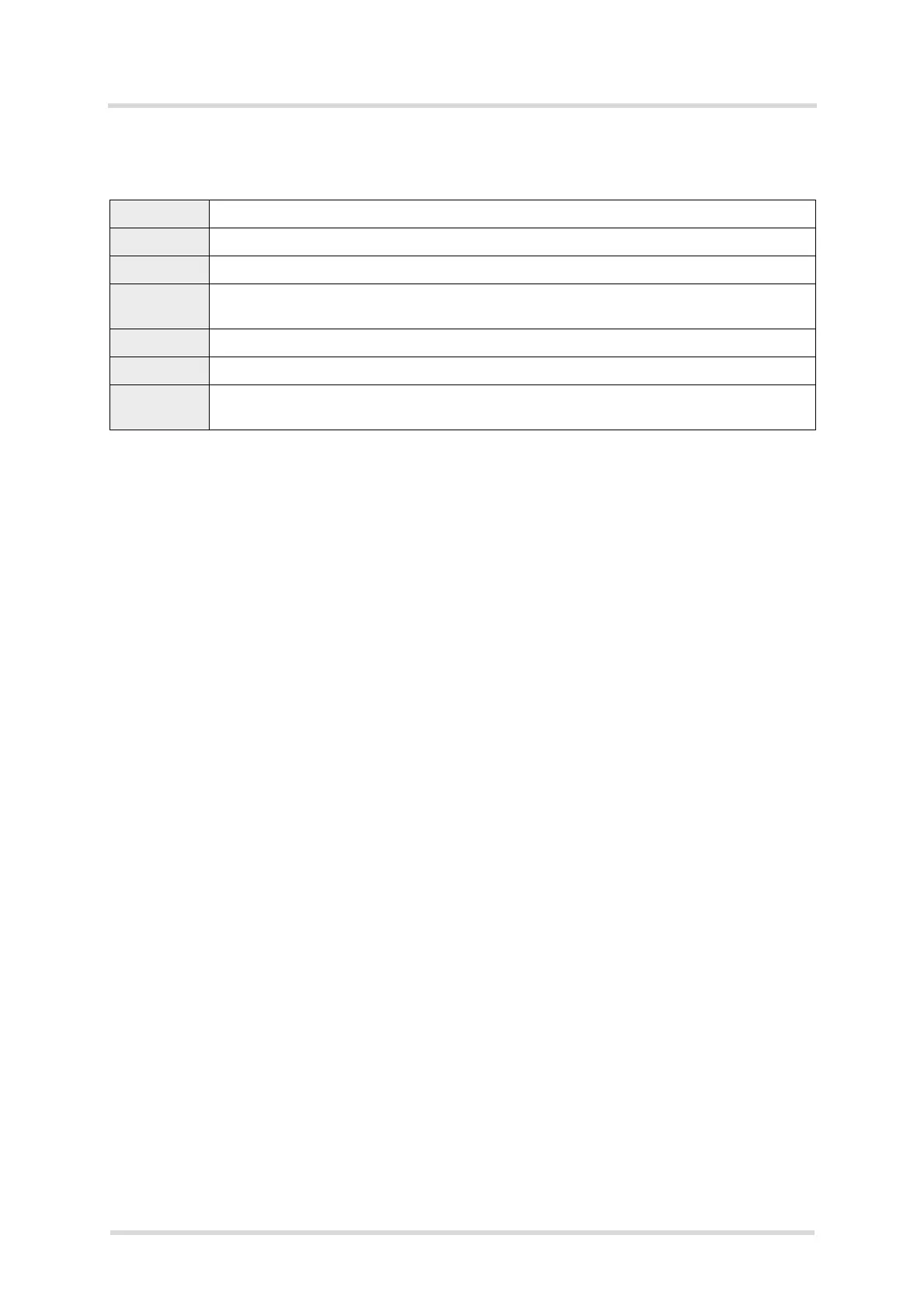

Command ADC_DSR0

Parameter <input/output>

Type Boolean

Range 0: Analog input (ADC1_IN)

1: Digital output (DSR0/SPI_CLK)

Default 0: Analog input (ADC1_IN)

Non-volatile Yes

Example WD= ADC_DSR0,0,0 // Configures the line to be analog input

WD= ADC_DSR0,1,1 // Configures the line to be digital output

Loading...

Loading...