Rev. 1.50 138 August 28, 2017 Rev. 1.50 139 August 28, 2017

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

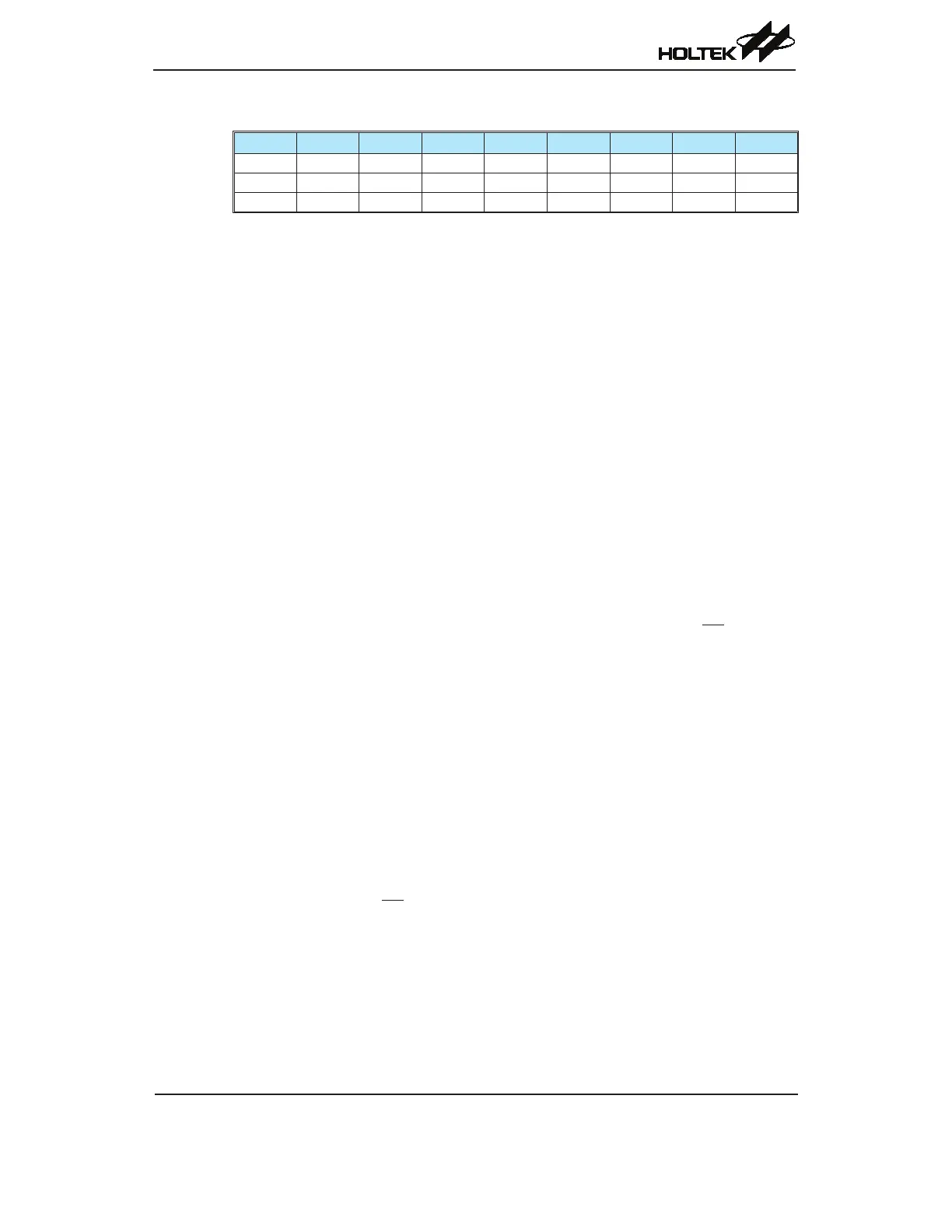

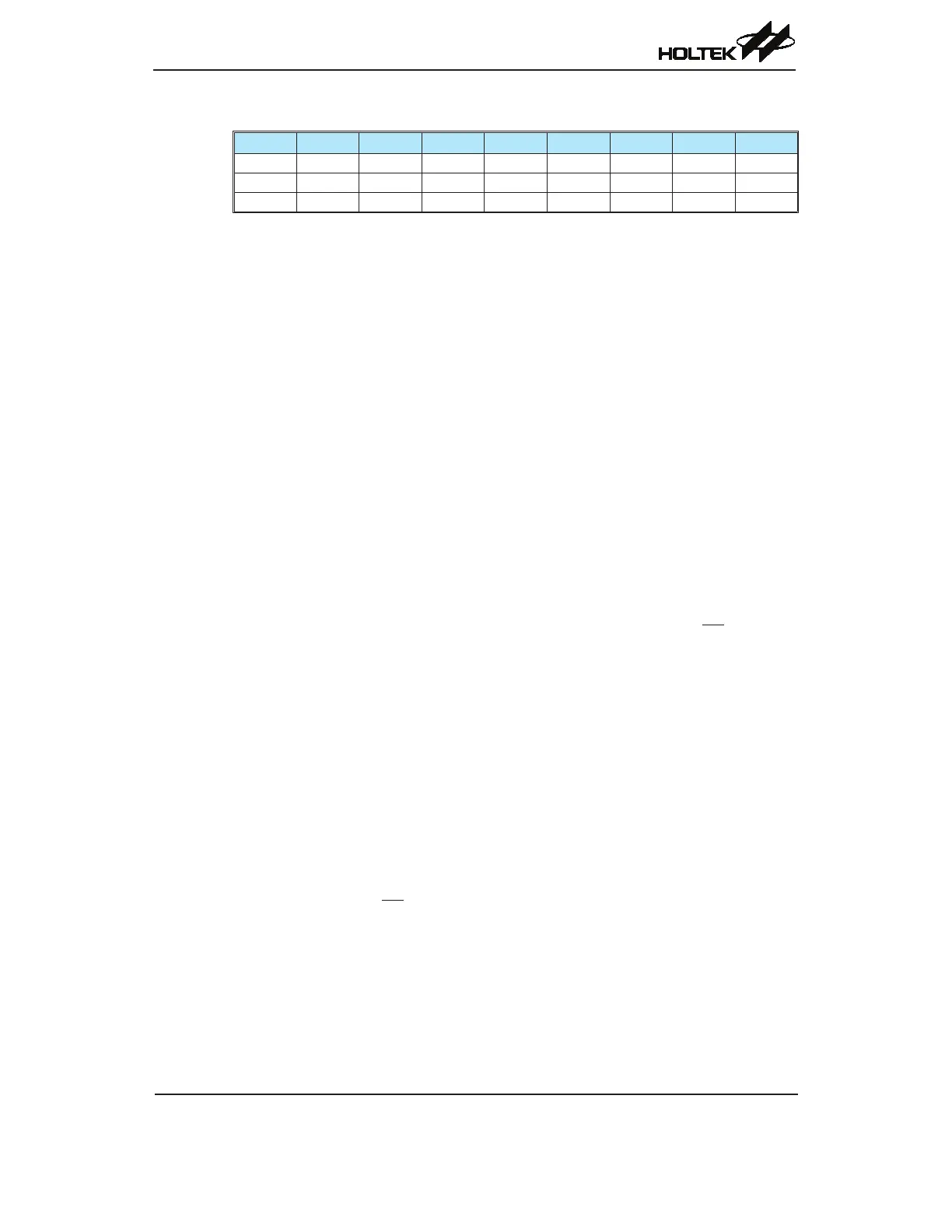

SIMC0 Register

Bit 7 6 5 4 3 2 1 0

Name SIM2 SIM1 SIM0 — SIMDEB1 SIMDEB0 SIMEN SIMICF

R/W R/W R/W R/W — R/W R/W R/W R/W

POR 1 1 1 — 0 0 0 0

Bit7~5 SIM2~SIM0:SIMOperatingModeControl

000:SPImastermode;SPIclockisf

SYS

/4

001:SPImastermode;SPIclockisf

SYS

/16

010:SPImastermode;SPIclockisf

SYS

/64

011:SPImastermode;SPIclockisf

TBC

100:SPImastermode;SPIclockisTM1CCRPmatchfrequency/2

101:SPIslavemode

110:I

2

Cslavemode

111:NonSIMfunction

ThesebitssetuptheoveralloperatingmodeoftheSIMfunction.Aswellasselecting

iftheI

2

CorSPIfunction,theyareusedtocontroltheSPIMaster/Slaveselectionand

theSPIMasterclockfrequency.TheSPIclockisafunctionofthesystemclockbut

canalsobechosentobesourcedfromTM1.IftheSPISlaveModeisselectedthenthe

clockwillbesuppliedbyanexternalMasterdevice.

Bit4 Unimplemented,readas“0”

Bit3~2 SIMDEB1~SIMDEB0:I

2

CDebounceTimeSelection

00:Nodebounce

01:2systemclockdebounce

1x:4systemclockdebounce

Bit1 SIMEN:SIMEnableControl

0:Disable

1:Enable

Thebitistheoverallon/offcontrolfortheSIMinterface.WhentheSIMENbitis

clearedtozerotodisabletheSIMinterface,theSDI,SDO,SCKandSCS,orSDAand

SCLlineswilllosetheirSPIorI

2

CfunctionandtheSIMoperatingcurrentwillbe

reducedtoaminimumvalue.WhenthebitishightheSIMinterfaceisenabled.Ifthe

SIMisconguredtooperateasanSPIinterfaceviatheSIM2~SIM0bits,thecontents

oftheSPIcontrolregisterswillremainattheprevioussettingswhentheSIMENbit

changesfromlowtohighandshouldthereforeberstinitialisedbytheapplication

program.IftheSIMisconguredtooperateasanI

2

CinterfaceviatheSIM2~SIM0

bitsandtheSIMENbitchangesfromlowtohigh,thecontentsoftheI

2

Ccontrolbits

suchasHTXandTXAKwillremainattheprevioussettingsandshouldthereforebe

rstinitialisedbytheapplicationprogramwhiletherelevantI

2

CagssuchasHCF,

HAAS,HBB,SRWandRXAKwillbesettotheirdefaultstates.

Bit0 SIMICF:SIMIncompleteFlag

0:SIMincompleteconditionnotoccurred

1:SIMincompleteconditionoccured

ThisbitisonlyavailablewhentheSIMisconguredtooperateinanSPIslavemode.

IftheSPIoperatesintheslavemodewiththeSIMENandCSENbitsbothbeingset

to1buttheSCSlineispulledhighbytheexternalmasterdevicebeforetheSPIdata

transferiscompletelynished,theSIMICFbitwillbesetto1togetherwiththeTRF

bit.Whenthisconditionoccurs,thecorrespondinginterruptwilloccuriftheinterrupt

functionisenabled.However,theTRFbitwillnotbesetto1iftheSIMICFbitisset

to1bysoftwareapplicationprogram.

Loading...

Loading...