Rev. 1.50 140 August 28, 2017 Rev. 1.50 141 August 28, 2017

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

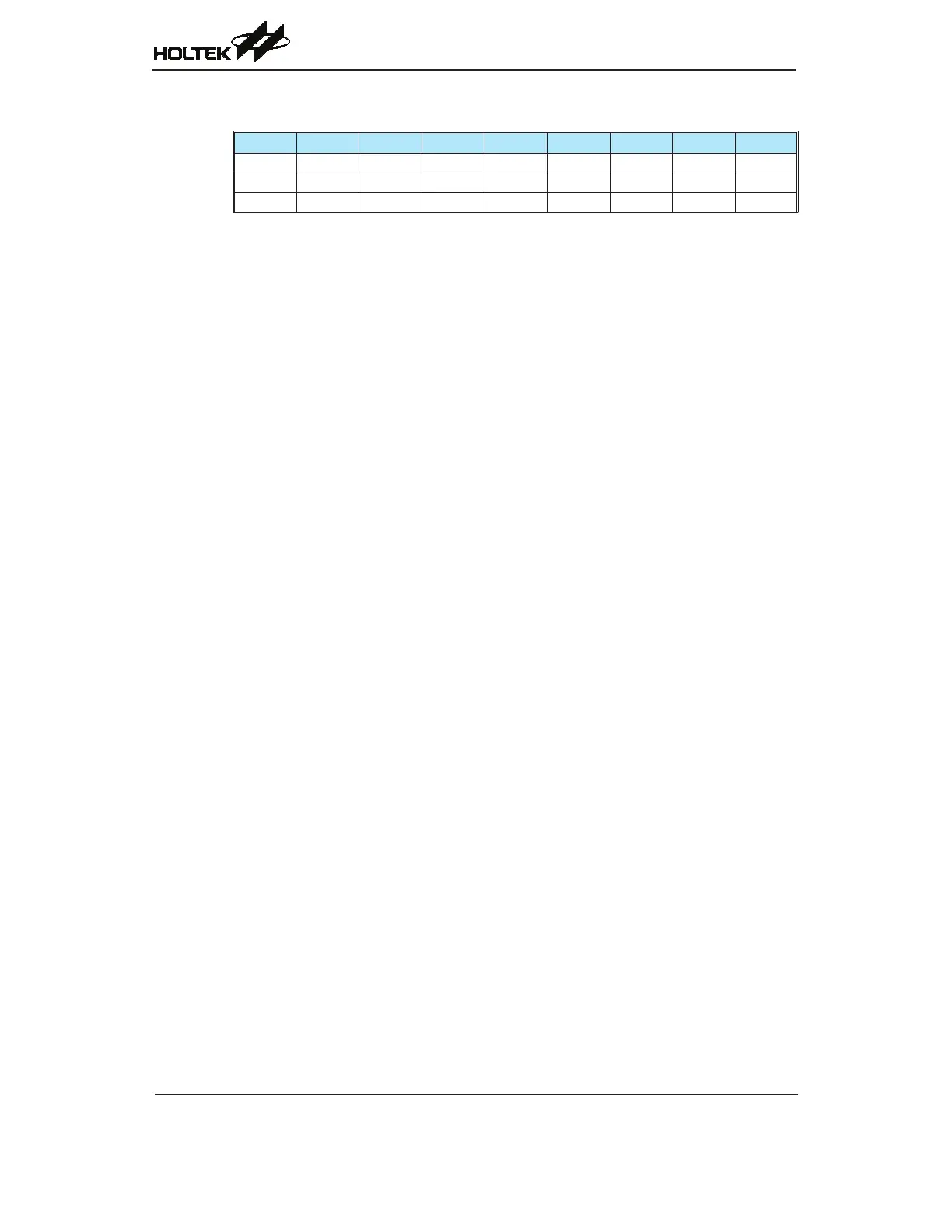

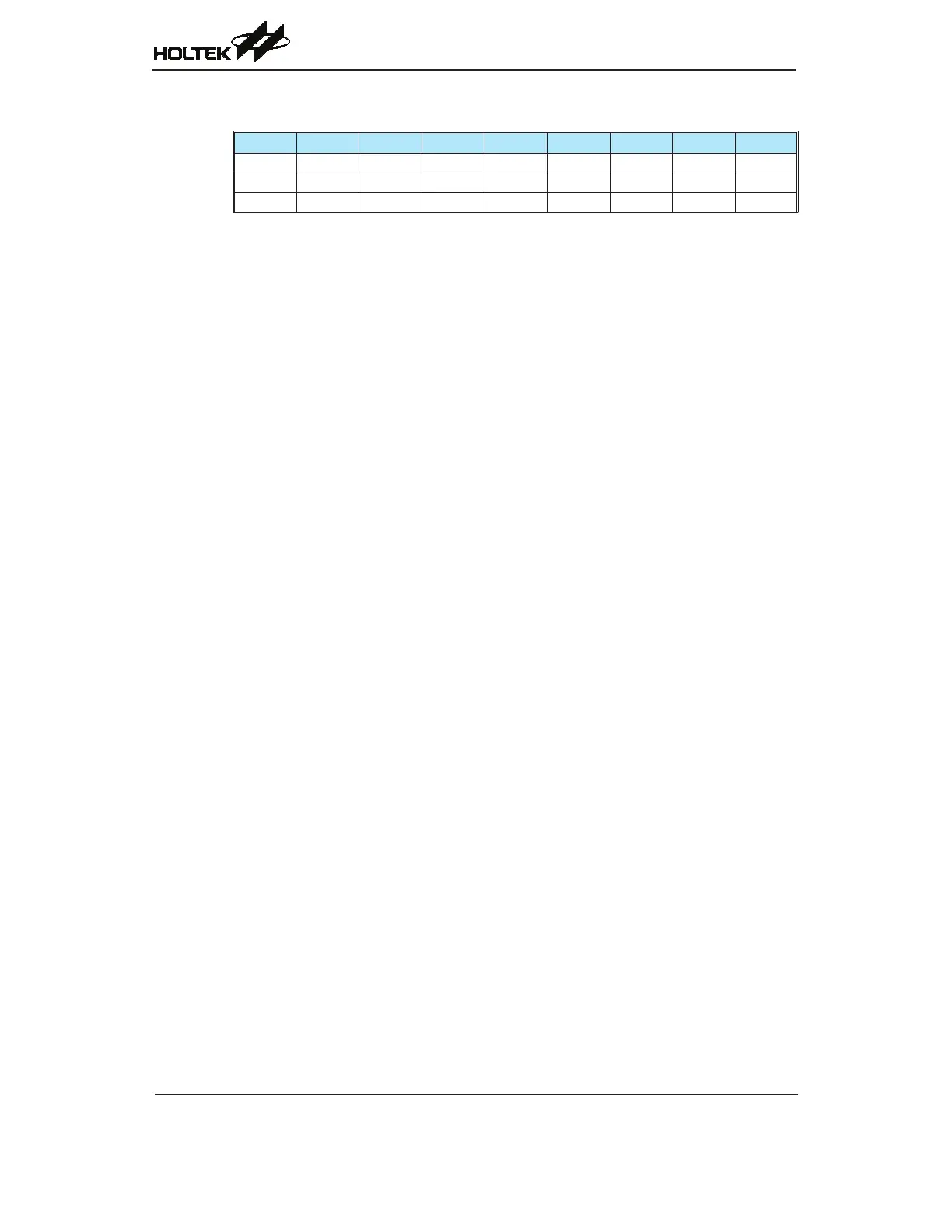

SIMC1 Register

Bit 7 6 5 4 3 2 1 0

Name HCF HAAS HBB HTX TXAK SRW IAMWU RXAK

R/W R R R R/W R/W R/W R/W R

POR 1 0 0 0 0 0 0 1

Bit7 HCF:I

2

CBusdatatransfercompletionag

0:Dataisbeingtransferred

1:Completionofan8-bitdatatransfer

TheHCFflagisthedatatransferflag.Thisflagwillbezerowhendataisbeing

transferred.Uponcompletionofan8-bitdatatransfertheflagwillgohighandan

interruptwillbegenerated.

Bit6 HAAS:I

2

CBusaddressmatchag

0:Notaddressmatch

1:Addressmatch

TheHAASagistheaddressmatchag.Thisagisusedtodetermineiftheslave

deviceaddressisthesameasthemastertransmitaddress.Iftheaddressesmatchthen

thisbitwillbehigh,ifthereisnomatchthentheagwillbelow.

Bit5 HBB:I

2

CBusbusyag

0:I

2

CBusisnotbusy

1:I

2

CBusisbusy

TheHBBflagistheI

2

Cbusyflag.Thisflagwillbe“1”whentheI

2

Cbusisbusy

whichwilloccurwhenaSTARTsignalisdetected.Theagwillbesetto“0”when

thebusisfreewhichwilloccurwhenaSTOPsignalisdetected.

Bit4 HTX:I

2

Cslavedevicetransmitter/receiverselection

0:Slavedeviceisthereceiver

1:Slavedeviceisthetransmitter

Bit3 TXAK:I

2

Cbustransmitacknowledgeag

0:Slavesendacknowledgeag

1:Slavedoesnotsendacknowledgeag

TheTXAKbitisthetransmitacknowledgeag.Aftertheslavedevicereceiptof8-bits

ofdata,thisbitwillbetransmittedtothebusonthe9thclockfromtheslavedevice.

TheslavedevicemustalwayssetTXAKbitto“0”beforefurtherdataisreceived.

Bit2 SRW:I

2

Cslaveread/writeag

0:Slavedeviceshouldbeinreceivemode

1:Slavedeviceshouldbeintransmitmode

TheSRWflagistheI

2

CSlaveRead/Writeflag.Thisflagdetermineswhether

themasterdevicewishestotransmitorreceivedatafromtheI

2

Cbus.Whenthe

transmittedaddressandslaveaddressismatch,thatiswhentheHAASagissethigh,

theslavedevicewillchecktheSRWagtodeterminewhetheritshouldbeintransmit

modeorreceivemode.IftheSRWagishigh,themasterisrequestingtoreaddata

fromthebus,sotheslavedeviceshouldbeintransmitmode.WhentheSRWflag

iszero,themasterwillwritedatatothebus,thereforetheslavedeviceshouldbein

receivemodetoreadthisdata.

Bit1 IAMWU:I

2

CAddressMatchWake-Upcontrol

0:Disable

1:Enable–mustbeclearedbytheapplicationprogramafterwake-up

Thisbitshouldbesetto1toenabletheI

2

CaddressmatchwakeupfromtheSLEEP

orIDLEMode.IftheIAMWUbithasbeensetbeforeenteringeithertheSLEEPor

IDLEmodetoenabletheI

2

Caddressmatchwakeup,thenthisbitmustbeclearedby

theapplicationprogramafterwake-uptoensurecorrectiondeviceoperation.

Loading...

Loading...