Rev. 1.50 46 August 28, 2017 Rev. 1.50 47 August 28, 2017

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

IDLE1 Mode

TheIDLE1ModeisenteredwhenanHALTinstructionisexecutedandwhentheIDLENbitinthe

SMODregisterishighandtheFSYSONbitintheCTRLregisterishigh.IntheIDLE1Modethe

systemoscillatorwillbeinhibitedfromdrivingtheCPUbutmaycontinuetoprovideaclocksource

tokeepsomeperipheralfunctionsoperationalsuchastheWatchdogTimerandTMs.IntheIDLE1

Mode,thesystemoscillatorwillcontinuetorun,andthissystemoscillatormaybehighspeedorlow

speedsystemoscillator.

Control Registers

Asingleregister,SMOD,isusedforoverallcontroloftheinternalclockswithinthedevices.

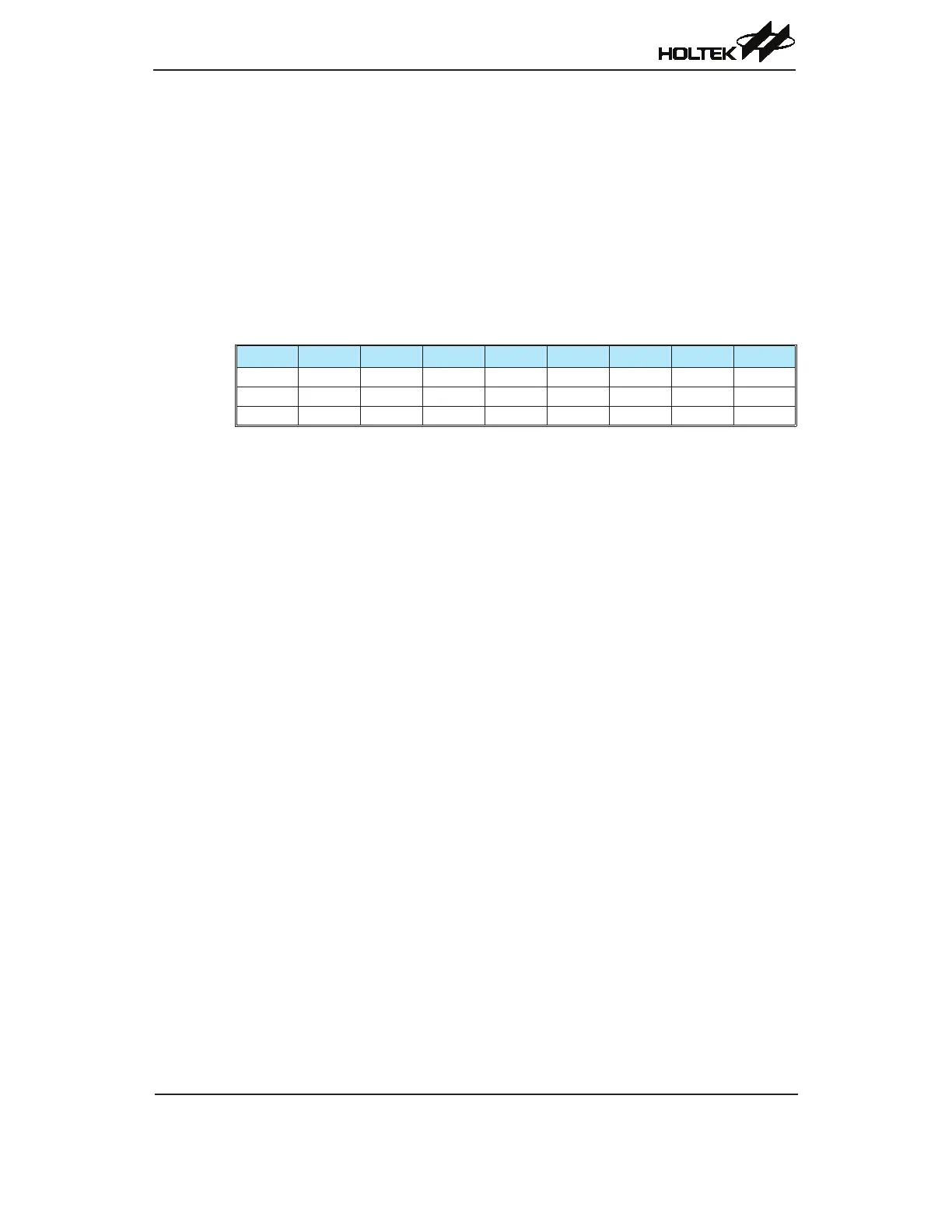

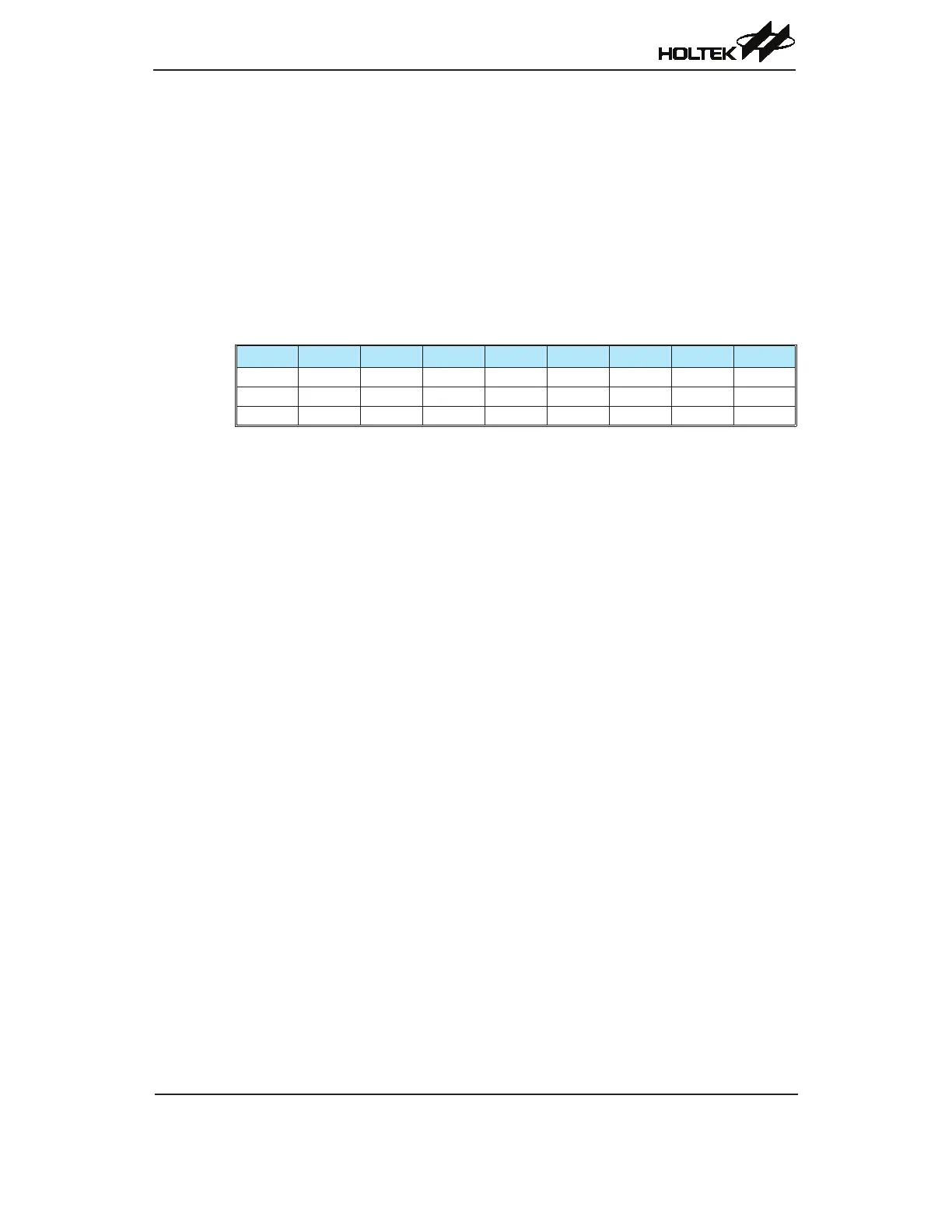

SMOD Register

Bit 7 6 5 4 3 2 1 0

Name CKS2 CKS1 CKS0 FSTEN LTO HTO IDLEN HLCLK

R/W R/W R/W R/W R/W R R R/W R/W

POR 0 0 0 0 0 0 1 1

Bit7~5 CKS2~CKS0:SystemclockselectionwhenHLCLKis“0”

000:f

SUB

001:f

SUB

010:f

H

/64

011:f

H

/32

100:f

H

/16

101:f

H

/8

110:f

H

/4

111:f

H

/2

Thesethreebitsareusedtoselectwhichclockisusedasthesystemclocksource.In

additiontothesystemclocksource,whichcanbeeithertheLXTorLIRC,adivided

versionofthehighspeedsystemoscillatorcanalsobechosenasthesystemclock

source.

Bit4 FSTEN:FastWake-upControl(onlyforHXT)

0:Disable

1:Enable

ThisistheFastWake-upControlbitwhichdeterminesifthef

SUB

clocksourceis

initiallyusedafterthedevicewakesup.Whenthebitishigh,thef

SUB

clocksourcecan

beusedasatemporarysystemclocktoprovideafasterwakeuptimeasthef

SUB

clock

isavailable.

Bit3 LTO :Lowspeedsystemoscillatorreadyag

0:Notready

1:Ready

Thisisthelowspeedsystemoscillatorreadyagwhichindicateswhenthelowspeed

systemoscillatorisstableafterpoweronresetorawake-uphasoccurred.Theag

willbelowwhenintheSLEEP0Modebutafterawake-uphasoccurred,theagwill

changetoahighlevelafter128clockcyclesiftheLXToscillatorisusedand1~2

clockcyclesiftheLIRCoscillatorisused.

Loading...

Loading...