Baseband Section Service Manual

10

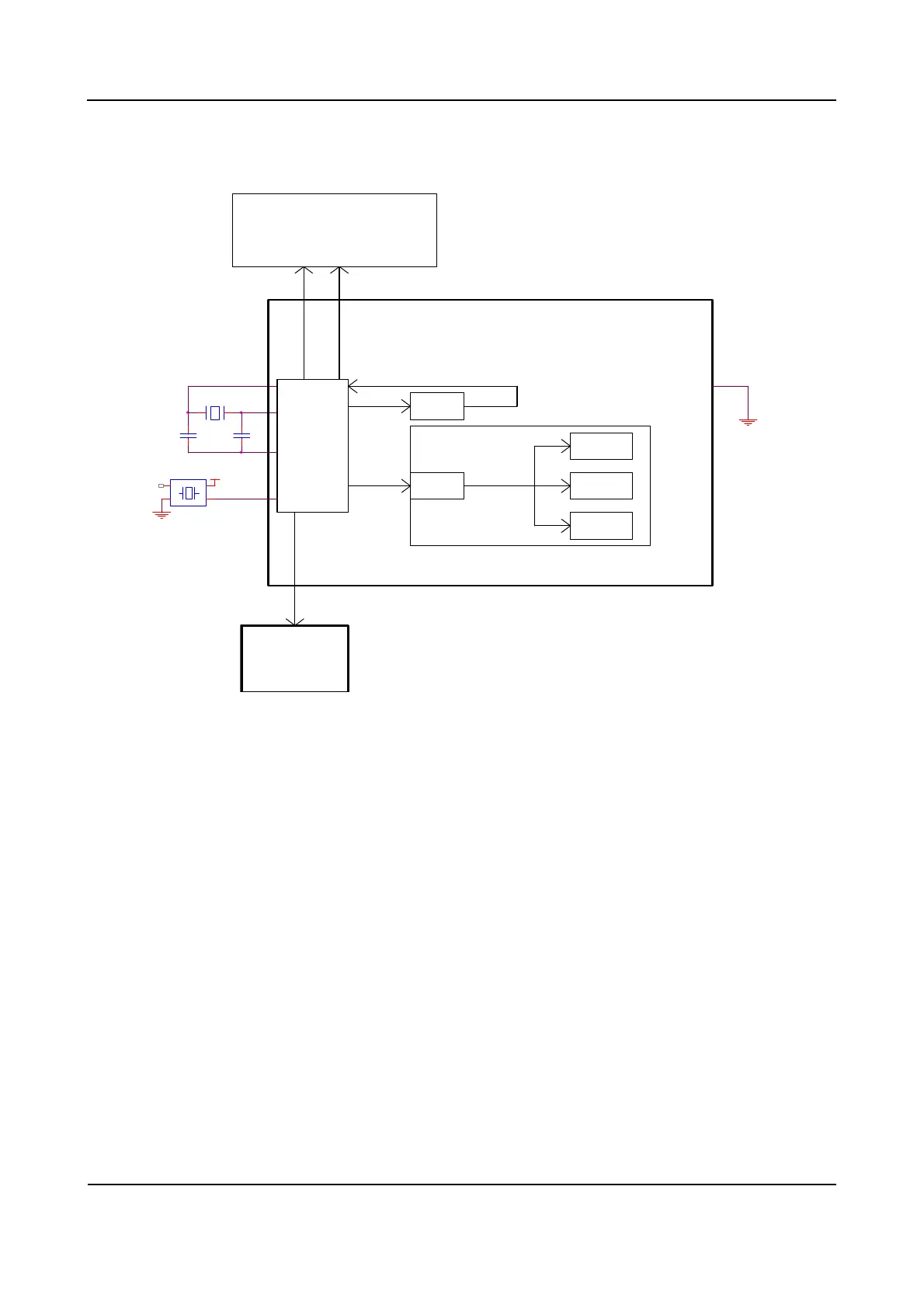

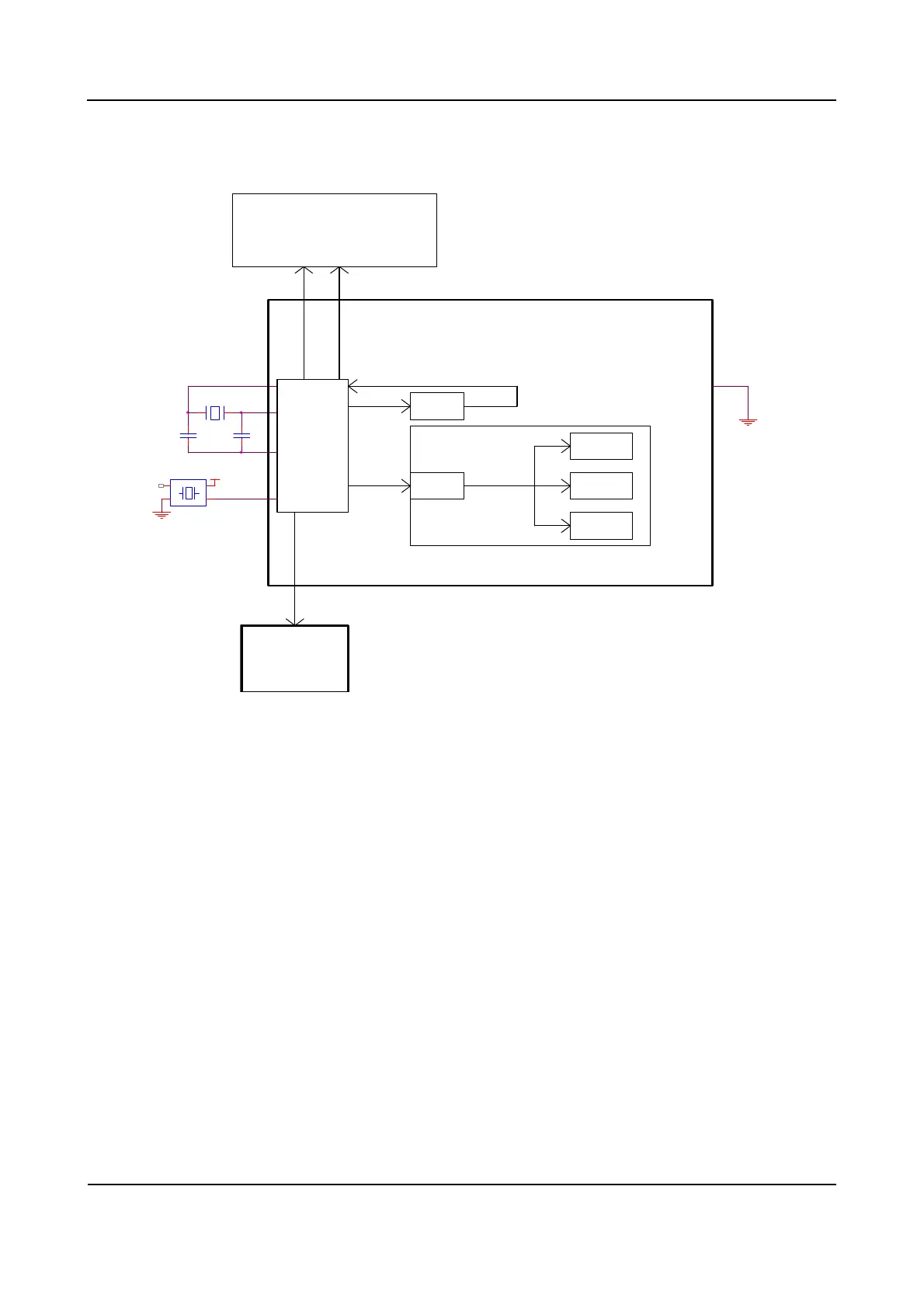

3.2.3 Clock

X2 01

32.768KHz

1 2

20pF 20pF

APLL

ULPD

96MHz

DPLL1

OSC32K_OUT

OSC32K_IN

OSC1_OUT

OSC1_IN

CK_REF

19.2MHz

ARM_CK

DSP_CK

TC_CK

MCLK

BCLK

CLK_32K_OUT

OMAP3.2

ULPD_PLL_CLK

OMAP5912

TLV320AIC29

19.2MHz

MCLK

Option board

CLK-OPT

CLK-32K-OUT

U201

U821

19.2MHz

32kHz

CLK32K_IN

VSS(Y13)

VCC

VCC

OUT

VCONT

GND

X20 3

TCXO 19.2MHz

1

2 3

4

Figure 3-6 Diagram of Baseband Clock

Input Clock

32K Clock: It is also called “sleep clock” and is mainly used for timing and sleeping of the system.

19.2MHz Clock: It is mainly used to provide input clock for APLL and DPLL.

Output Clock

Three output clocks are provided: MCLK, BCLK and CLK32K_OUT. MCLK provides 19.2MHz clock to

the audio codec; BCLK provides 19.2MHz clock to the option board; and CLK32K_OUT provides 32

KHz clock to the option board.

Loading...

Loading...