•

fp32_adder_inexact

•

fp32_adder_overflow

•

fp32_adder_underflow

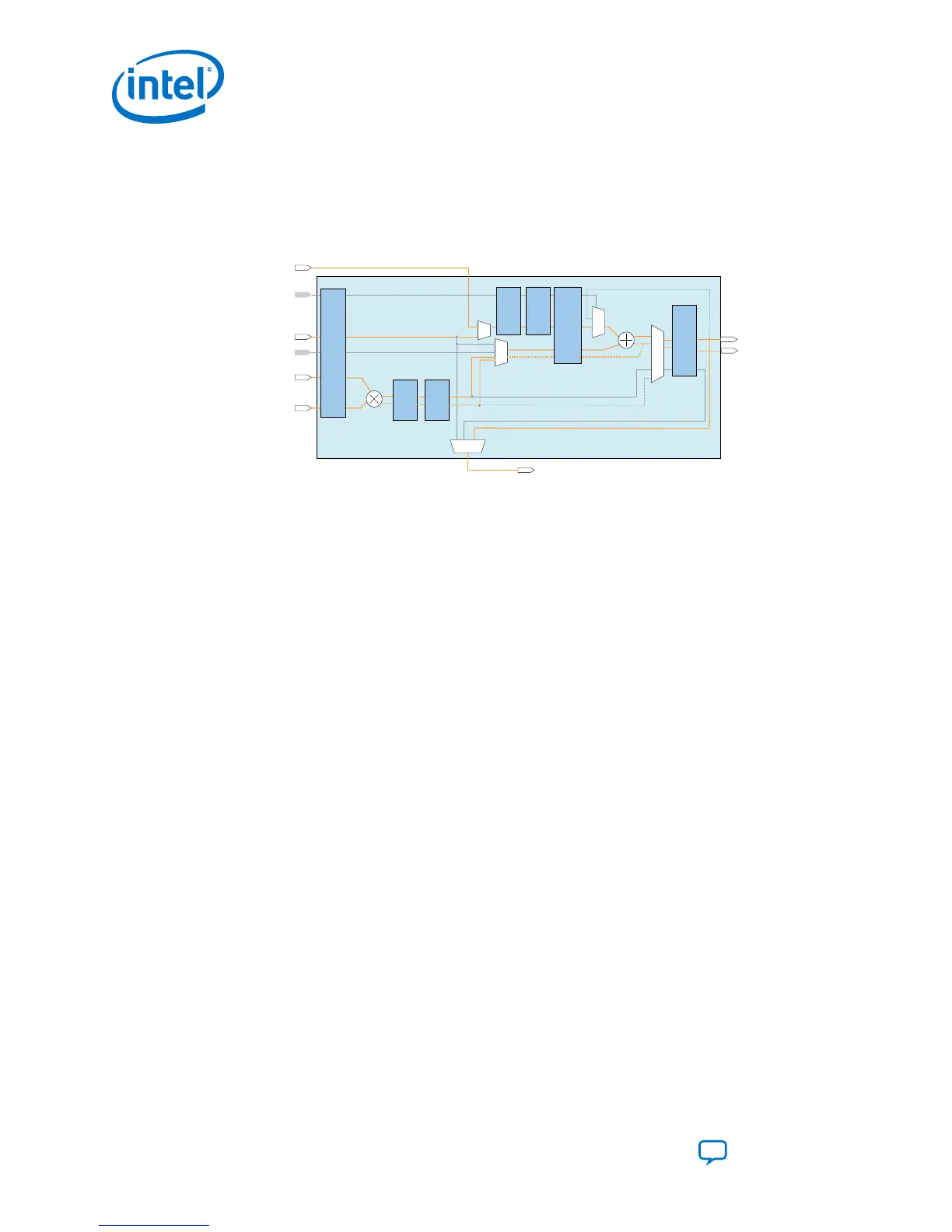

Figure 39. Multiply-Add or Multiply-Subtract Mode for Intel Agilex Devices

fp32_chainout[31:0]

fp32_chainin[31:0]

accumulate

fp32_adder_a[31:0]

fp32_result[31:0]

Multiplier

Adder

*Pipeline

Register

Bank

*Pipeline

Register

Bank

Register

Bank

*Pipeline

Register

Bank

*Pipeline

Register

Bank

fp32_mult_invalid

fp32_mult_inexact

fp32_mult_overflow

fp32_mult_underflow

fp32_adder_invalid

fp32_adder_inexact

fp32_dder_overflow

fp32_adder_underflow

*Pipeline

*This block diagram shows the functional representation of the DSP block.

The pipeline registers are embedded within the various circuits of the DSP block.

Output

Register

Bank

Input

Register

Bank

fp32_adder_b[31:0]

fp32_mult_a[31:0]

fp32_mult_b[31:0]

3.2.3.2. Direct Vector Dot Product

The following figures shows the combination of DSP blocks to create direct vector dot

product. For FP32 single-precision floating-point arithmetic, the direct vector dot

product consists of:

• Multiply-add and subtract mode with chainin parameter turned on

• Vector one

• Vector two

3. Intel Agilex Variable Precision DSP Blocks Operational Modes

UG-20213 | 2019.04.02

Intel

®

Agilex

™

Variable Precision DSP Blocks User Guide

Send Feedback

56

Loading...

Loading...