4.2.1.1. FP32 Operation Modes Supported Register Configurations

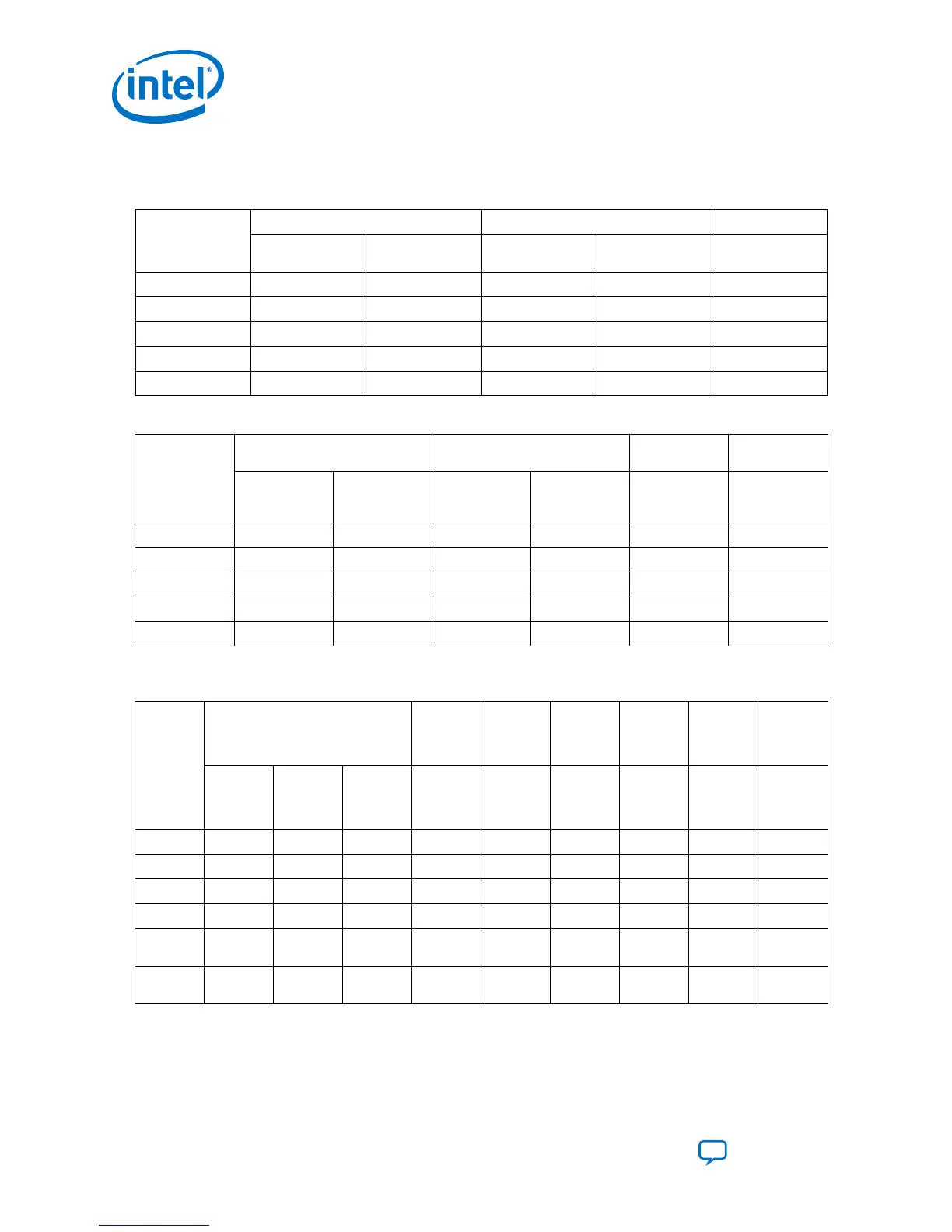

Table 26. Supported Register Configurations For FP32 Multiplication Mode

Latency Input Register Pipeline Register Output Register

fp32_mult_a_clk

en

fp32_mult_b_clk

en

mult_pipeline_cl

ken

mult_2nd_pipelin

e_clken

output_clken

0 Disable Disable Disable Disable Disable

1 Enable Enable Disable Disable Disable

1 Disable Disable Disable Disable Enable

2 Enable Enable Disable Enable Enable

≥3 Disable Enable Disable, enable Enable Enable

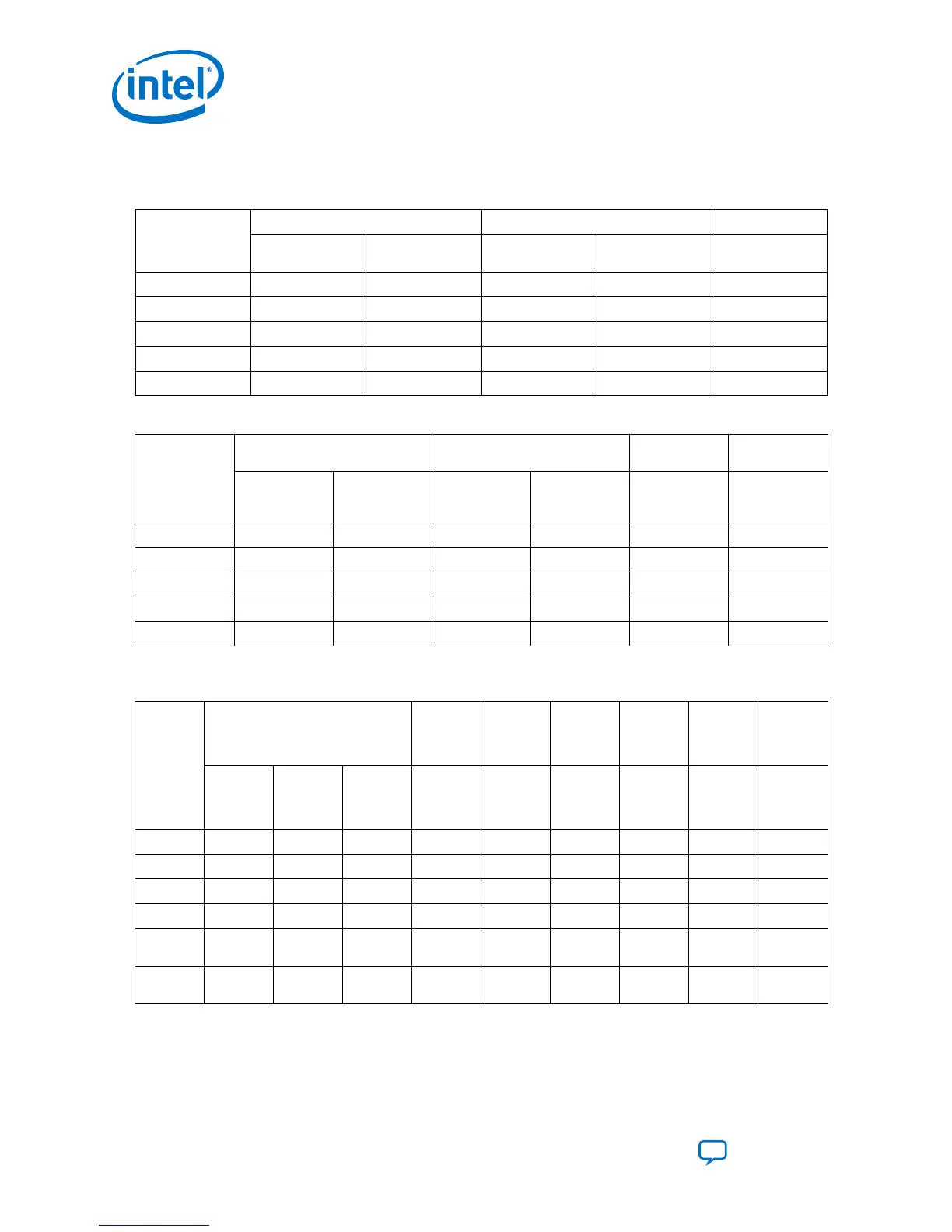

Table 27. Supported Register Configurations For FP32 Addition or Subtraction Mode

Latency Data Input Register Pipeline Register Adder Input

Register

Output

Register

fp32_adder_a

_clken

fp32_adder_b

_clken

fp32_adder_a

_chainin_pl_cl

ken

fp32_adder_a

_chainin_2nd_

pl_clken

adder_input_c

lken

output_clken

0 Disable Disable Disable Disable Disable Disable

1 Enable Enable Disable Disable Disable Disable

1 Disable Disable Disable Disable Disable Enable

2 Enable Enable Disable Disable Disable Enable

≥3 Enable Enable Disable, enable Disable, enable Enable Enable

Table 28. Supported Register Configurations For FP32 Multiplication with Addition or

Subtraction Mode

Latency Data Input Register Adder 1st

Pipeline

Register

Adder

2nd

Pipeline

Register

Multiplier

1st

Pipeline

Register

Multiplier

2nd

Pipeline

Register

Adder

Input

Register

Output

Register

fp32_add

er_a_clke

n

fp32_mul

t_a_clken

fp32_mul

t_b_clken

fp32_add

er_a_chai

nin_pl_cl

ken

fp32_add

er_a_chai

nin_2nd_

pl_clken

mult_pipe

line_clke

n

mult_2nd

_pipeline

_clken

adder_inp

ut_clken

output_cl

ken

0 Disable Disable Disable Disable Disable Disable Disable Disable Disable

1 Enable Enable Enable Disable Disable Disable Disable Disable Disable

1 Disable Disable Disable Disable Disable Disable Disable Disable Enable

2 Enable Enable Enable Disable Disable Disable Disable Disable Enable

≥3 Enable Enable Enable Disable,

enable

Disable,

enable

Disable Disable Enable Enable

≥4 Enable Enable Enable Disable,

enable

Disable,

enable

Disable,

enable

Enable Enable Enable

4. Intel Agilex Variable Precision DSP Blocks Design Considerations

UG-20213 | 2019.04.02

Intel

®

Agilex

™

Variable Precision DSP Blocks User Guide

Send Feedback

68

Loading...

Loading...