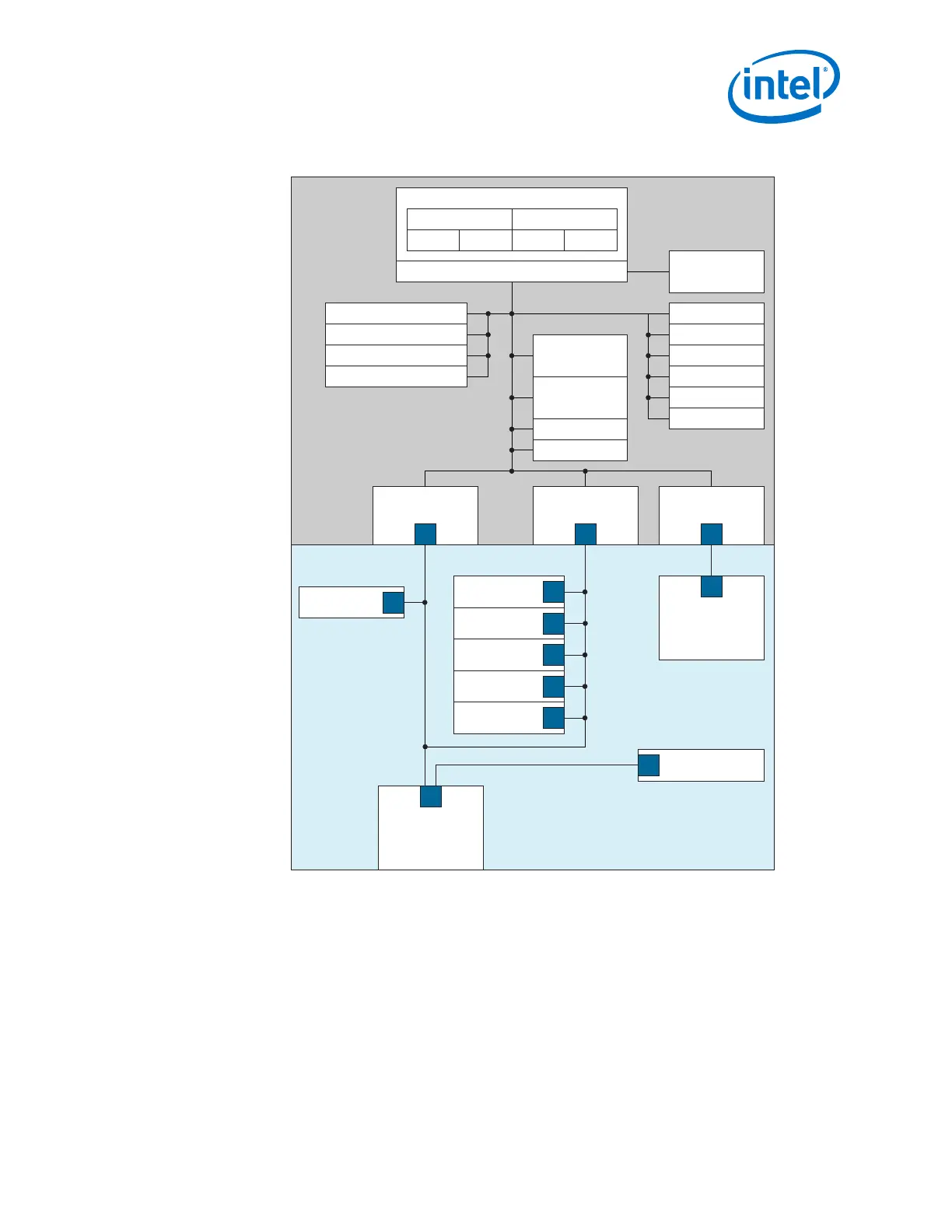

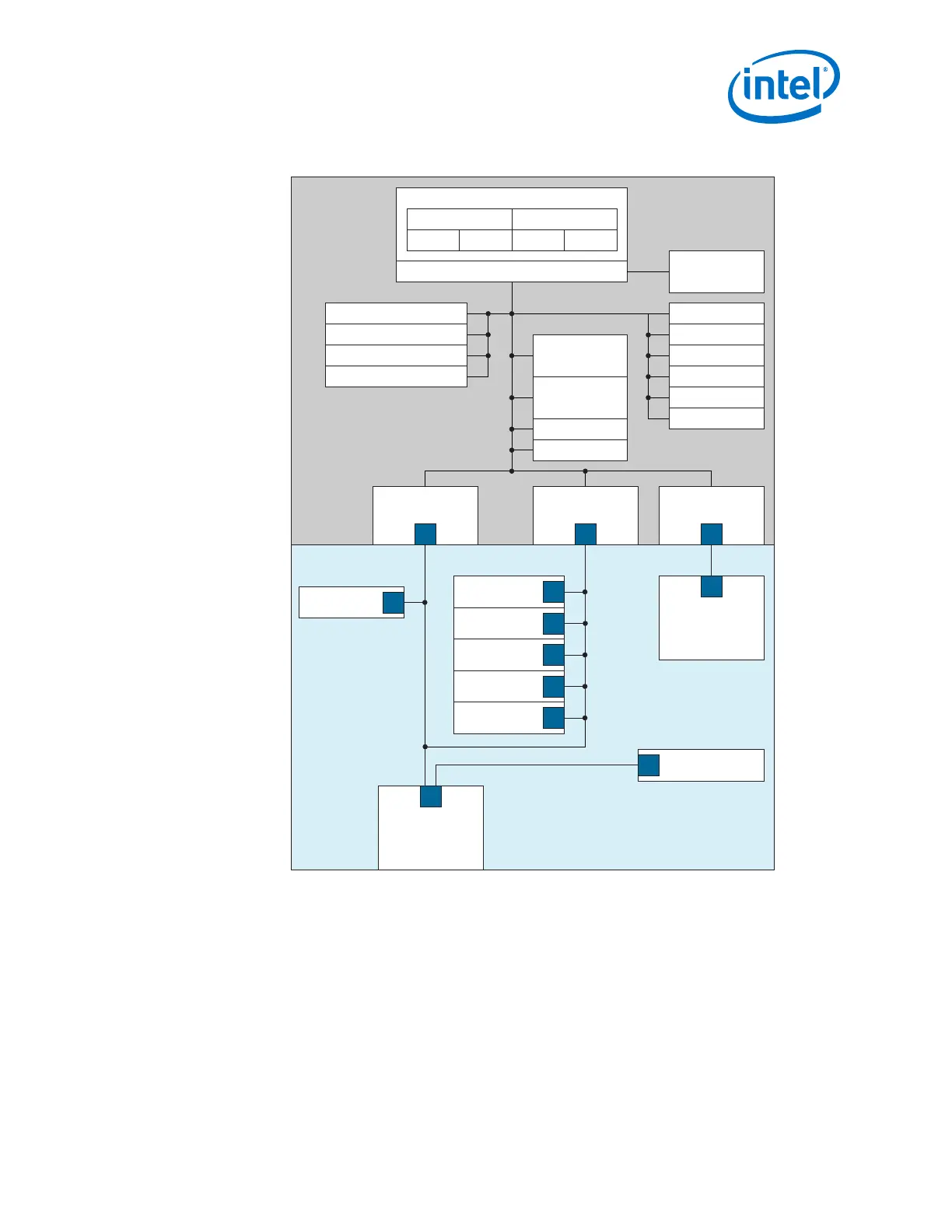

Figure 7. Cyclone V / Arria V SoC Golden Hardware Reference Design Overview

Trace Memory Controller

USB OTG

Gbps Ethernet

SD/MMC

QSPI

GPIO

I2C

UART

CAN

Timers

FPGA Manager

DMA

ROM

RAM 64 KB

L2 DDR

HPS-to-FPGA

M

Lightweight

HSP-to-FPGA

M

FPGA-to-HPS

S

System ID S

PIO LED S

PIO Button S

PIO DIP Switch S

JTAG UART S

On-Chip RAM S

Non-Secure

JTAG Master

(FPGA Only)

M

Interrupt CapturerS

Secure

JTAG Master

(HPS Only)

M

Hard Processor

System

FPGA Fabric

I-Cache D-Cache I-Cache D-Cache

CPU0 CPU1

ARM Coretex-A9 MPCore

The GHRD has a minimal set of peripherals in the FPGA fabric, because the HPS

provides a substantial selection of peripherals. HPS-to-FPGA and FPGA-to-HPS

interfaces are configured to a 64-bit data width.

GUIDELINE: Intel recommends that you use the latest GHRD as a baseline for

new SoC FPGA hardware projects. You may then modify the design to suit

your application ends.

The GHRD can be obtained from:

5. Embedded Software Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

51

Loading...

Loading...