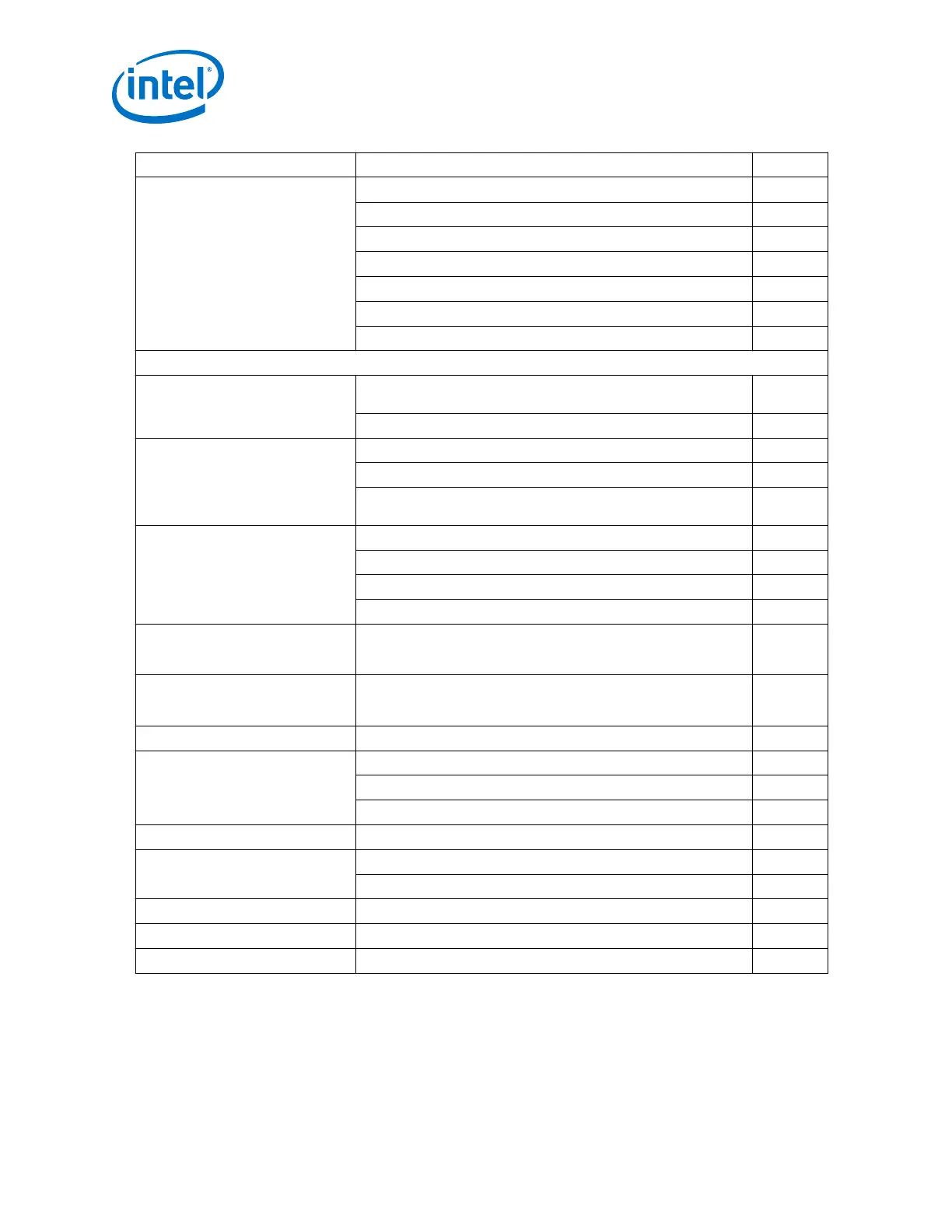

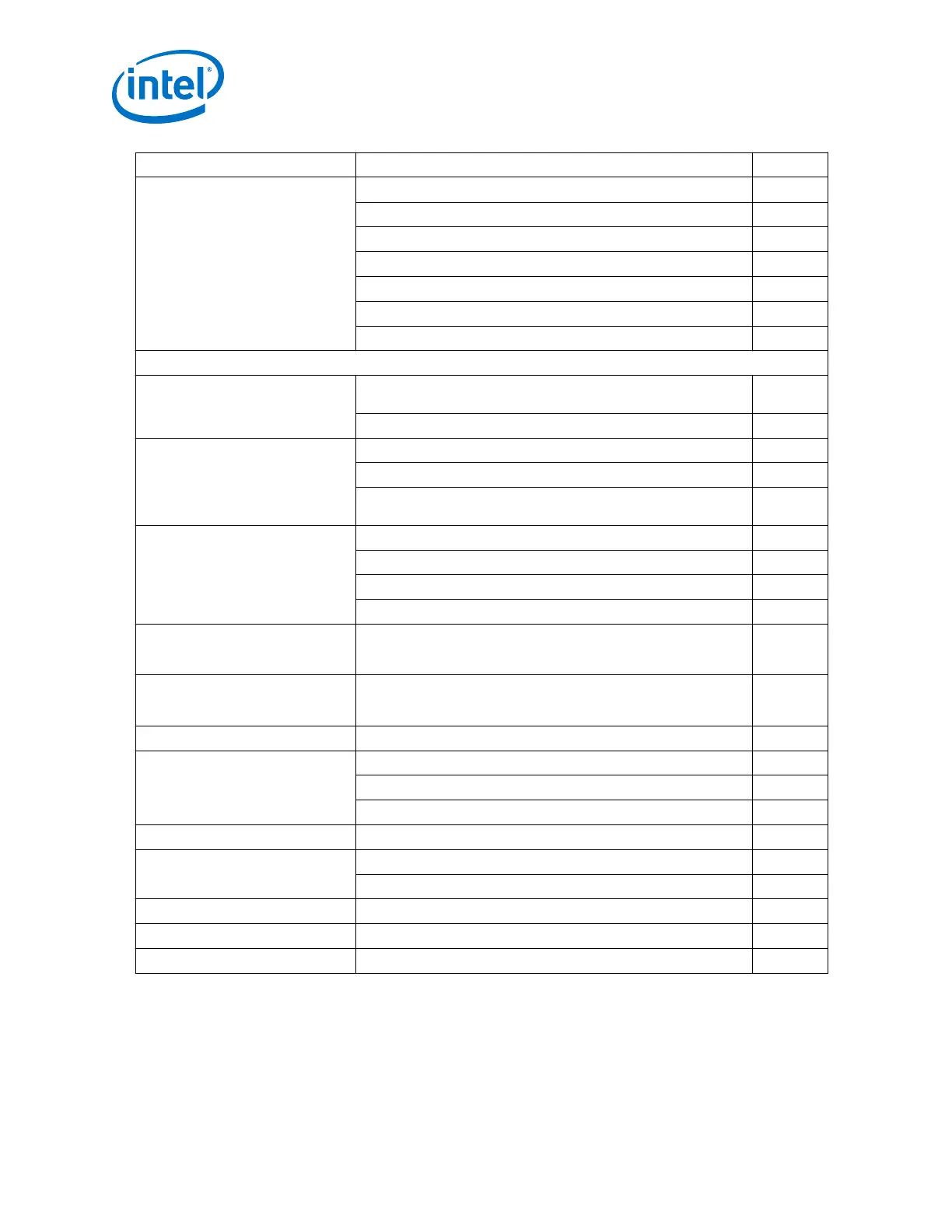

Step Title Links Check (X)

USB Interface Design Guidelines on page 43

QSPI Flash Interface Design Guidelines on page 44

SD/MMC and eMMC Card Interface Design Guidelines on page 45

NAND Flash Interface Design Guidelines on page 46

UART Interface Design Guidelines on page 46

I2C Interface Design Guidelines on page 47

SPI Interface Design Guidelines on page 47

Embedded Software Designer's Checklist for SoC FPGAs

Assemble the components of your

Software Development Platform

Assembling the Components of Your Software Development Platform

on page 49

Golden Hardware Reference Design on page 50

Select an Operating System (OS) for

your application

Linux or RTOS on page 52

Bare Metal on page 52

Using Symmetrical vs. Asymmetrical Multiprocessing (SMP vs. AMP)

Modes on page 53

Assemble your Software

Development Platform for Linux

Golden System Reference Design (GSRD) for Linux on page 54

GSRD for Linux Development Flow on page 54

GSRD for Linux Build Flow on page 55

Linux Device Tree Design Considerations on page 56

Assemble your Software

Development Platform for Bare-metal

Application

Assembling a Software Development Platform for a Bare-Metal

Application on page 57

Assemble your Software

Development Platform for Partner

OS/RTOS Application

Assembling your Software Development Platform for a Partner OS or

RTOS on page 58

Choose the Boot Loader Software Choosing Boot Loader Software on page 58

Selecting Software Tools for

Development, Debug and Trace

Select Software Build Tools on page 60

Select Software Debug Tools on page 60

Select Software Trace Tools on page 61

Board Bring Up Considerations Board Bring Up Considerations on page 28

Boot and Configuration Design

Considerations

Boot Design Considerations on page 28

Configuration on page 32

Flash Device Driver Considerations Flash Device Driver Design Considerations on page 61

HPS ECC Design Considerations HPS ECC Design Considerations on page 61

HPS SDRAM Considerations HPS SDRAM Considerations on page 63

1. Overview of the Design Guidelines for Cyclone

®

V SoC FPGAs and Arria

®

V SoC FPGAs

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

6

Loading...

Loading...