Intel

®

Ethernet Network Adapter E810-XXVDA4T

User Guide

50 646265-004

4. Verify if the outputs were set correctly

#dmesg

[19707.757036] ice 0000:18:00.1: Enabled recovered clock: pin C827_0-RCLKB

[19718.804404] ice 0000:18:00.0: <DPLL0> state changed to: unlocked, pin C827_0-

RCLKB

[19718.804920] ice 0000:18:00.0: <DPLL1> state changed to: unlocked, pin C827_0-

RCLKB

[19719.511845] ice 0000:18:00.0: Enabled recovered clock: pin C827_0-RCLKA

[19789.633771] ice 0000:18:00.0: <DPLL0> state changed to: locked, pin C827_0-

RCLKA

Note: Only enable SyncE on one adapter, either leader or follower is acceptable. If both are set,

users might run into sync loop issues.

5.6.3 ITU G.8264 ESMC messaging using synce4l

The synce4l application is implementing the G.8264 ESMC protocol.

1. Run synce4l:

# ./synce4l -f configs/synce4l.cfg -l 7 -m

Note: Refer to Section 5.10, “Example synce4l Configuration File for BC”.

Note: For GM mode, ensure that input_mode = external is used in the config file.

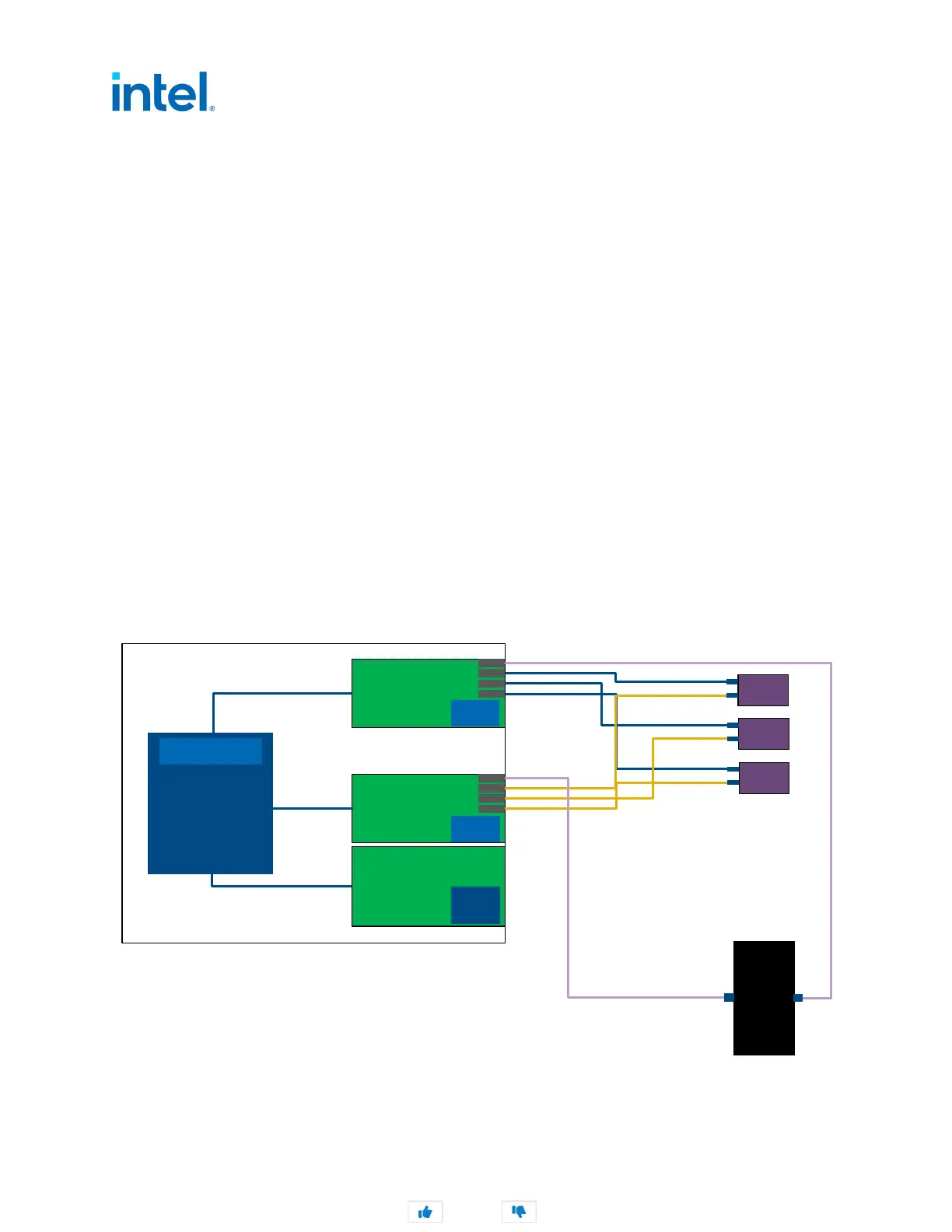

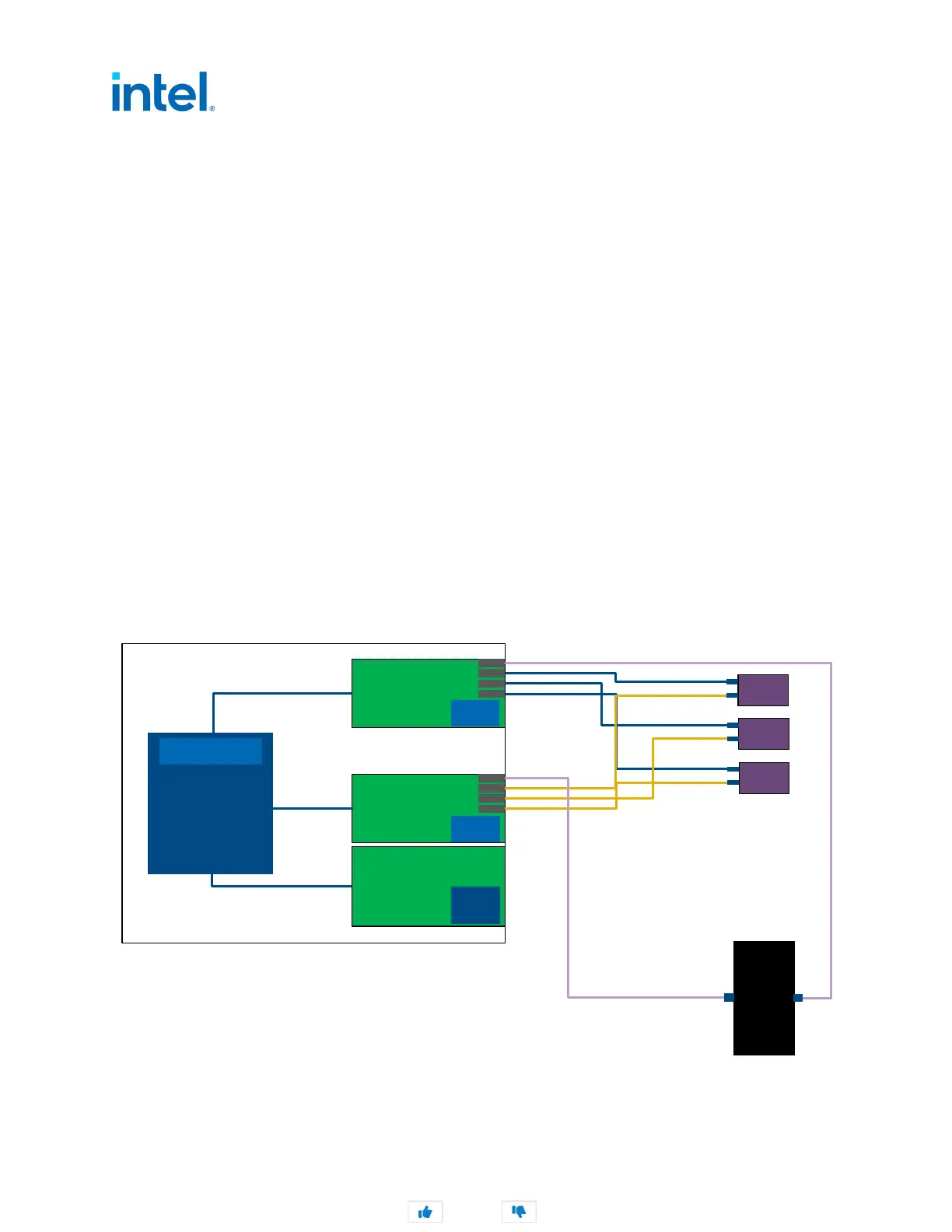

5.6.4 Two E810-XXVDA4T without GNSS Configuration

Figure 12 shows two E810-XXVDA4T in a system with a cell site router.

Figure 12. External Connections: Two E810-XXVDA4T without GNSS

Server

E810-XXVDA4T

E810-XXVDA4T

Mt. Bryce

CSR

RU

Gen4 x8

Gen4 x8

Gen3 x16

F

F

GM

L

F

L

L

MBC

Intel® vRAN

Accelerator ACC100

Adapter

GM

RU

RU

F

F

F

F

L

F

L

L

PHC1

PHC2

3

rd

Generation

Intel® Xeon®

Scalable

Processor

System Clock

Did this document help answer your questions?

Loading...

Loading...