523462 13

Intel Confidential

PCH SPI Flash Architecture

2.7 Hardware vs. Software Sequencing

Hardware and software sequencing are the two methods the PCH uses communicates

with the flash via programming registers for each of the three masters.

When utilizing software sequencing, BIOS needs to program the OPTYPE and OPMENU

registers respectively with the opcode it needs. It also defines how the system should

use each opcode. If the system needs a new opcode that has not been defined, then

BIOS can overwrite the OPTYPE and OPMENU register and define new functionality as

long as the FLOCKDN bits have not been set.

FPT as well as some BIOS implementation support software sequencing. Note: FPT

defaults to hardware sequencing.

Hardware sequencing has a predefined list of opcodes with only the erase opcode being

programmable. This mode is only available if the descriptor is present and valid. Intel

®

ME Firmware and Integrated LAN FW, and integrated LAN drivers all must use HW

sequencing, so BIOS must properly set up the PCH to account for this. The Host VSCC

registers and Intel Management Engine VSCC table have to be correctly configured for

BIOS, GbE and Intel

®

ME Firmware to have read/write access to SPI.

See Serial Peripheral Interface Memory Mapped Configuration Registers in

Broadwell PCH-LP Family External Design Specification (EDS) for more details.

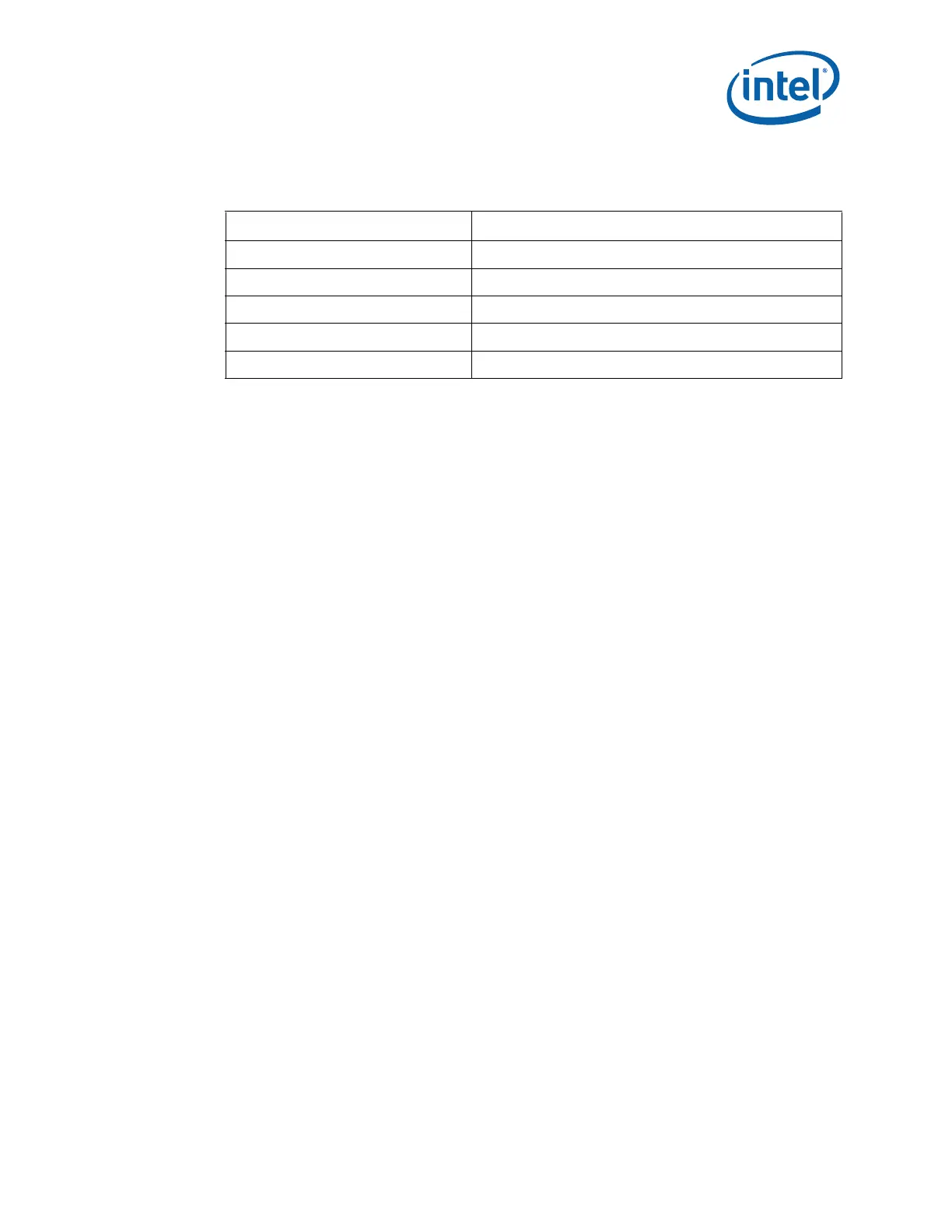

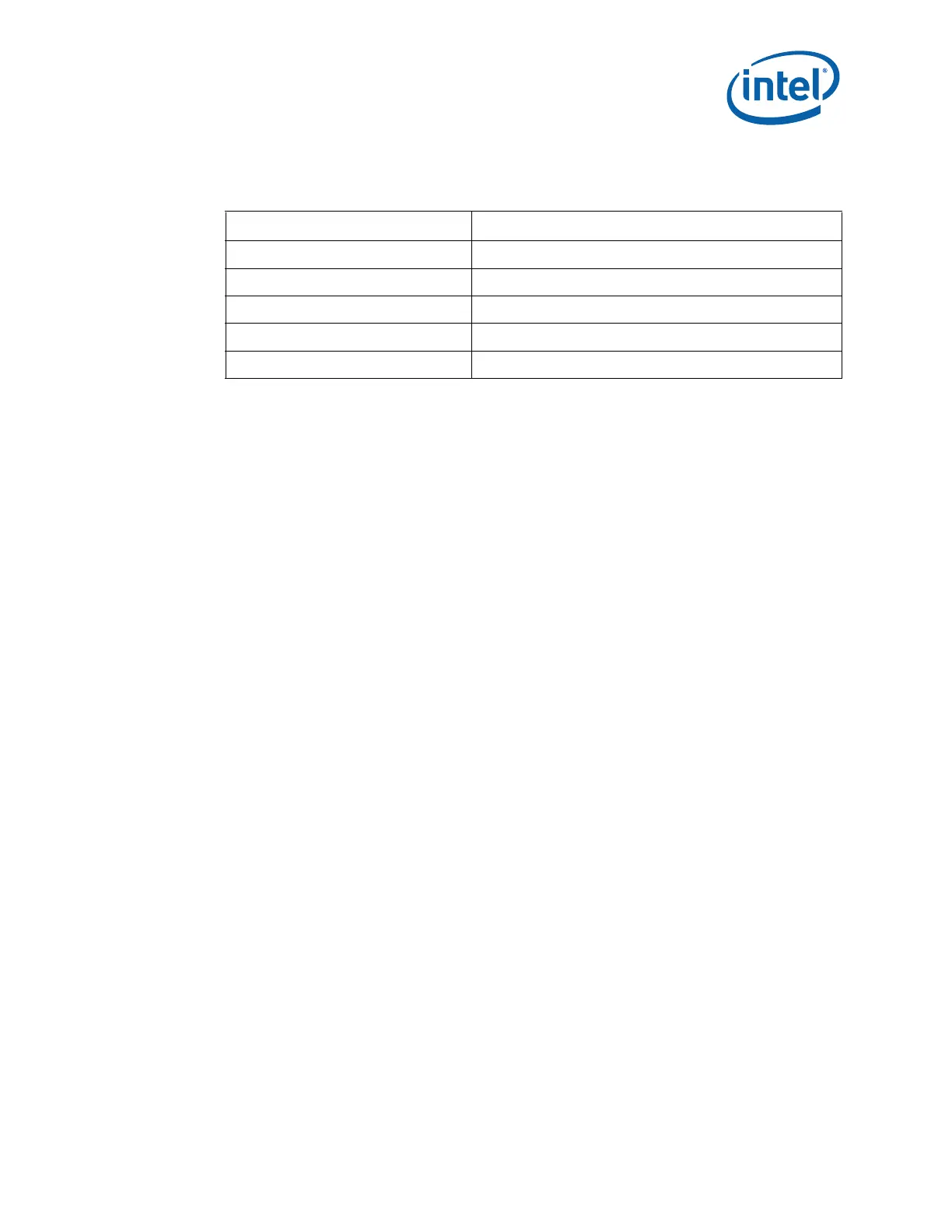

Table 2-1. Region Size vs. Erase Granularity of Flash Components

Regions Size with uniform 4 KB blocks

Descriptor 4 KB

GbE 8 KB

Platform Data Region

Varies by platform

BIOS

Varies by platform

ME

Varies by platform and configuration

Loading...

Loading...