523462 89

Intel Confidential

APPENDIX A - Descriptor Configuration

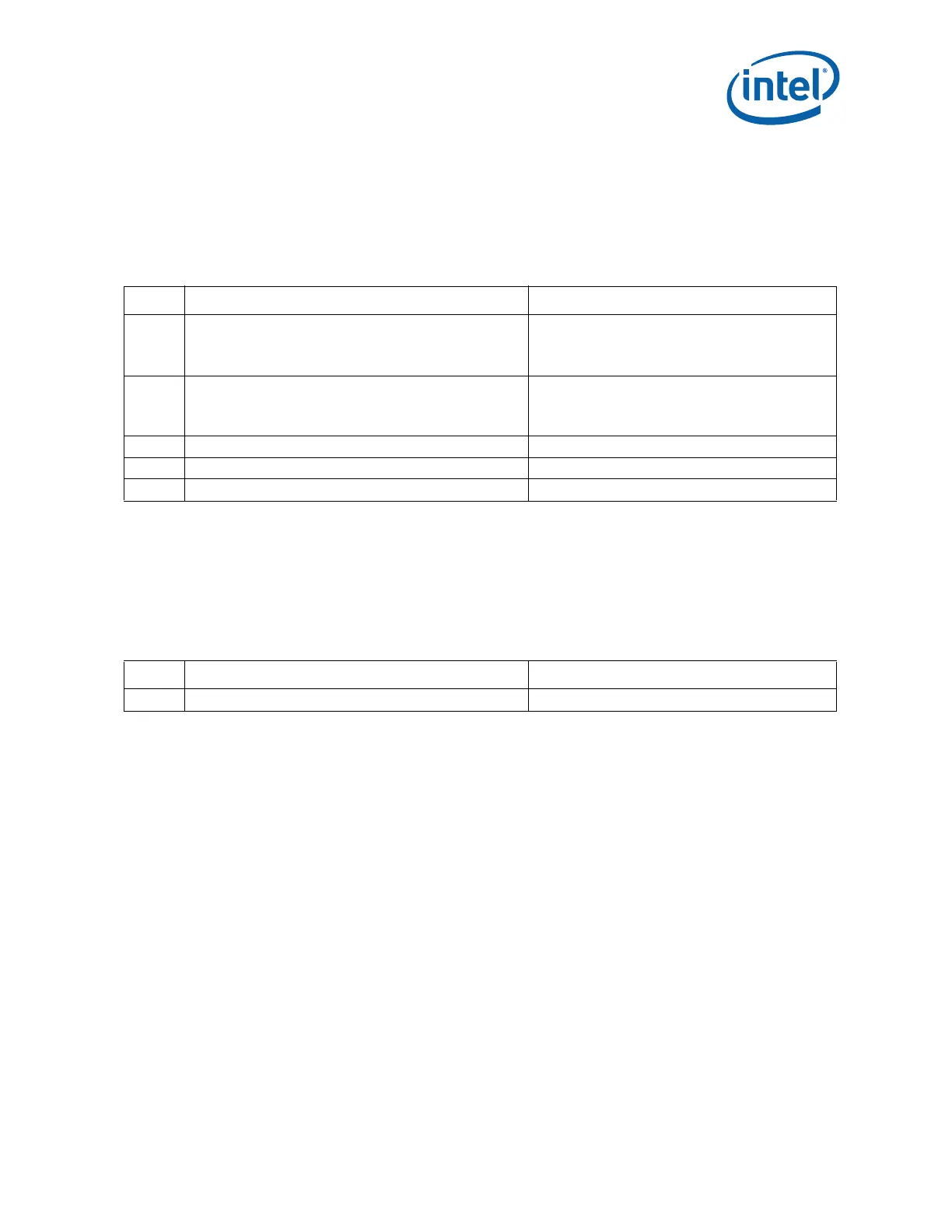

A.21 PCHSTRP19—Strap 19 Record (Flash Descriptor

Records)

Flash Address: FPSBA + 04Ch Size: 32 bits

Default Flash Address: 14Ch

Recommended Value:

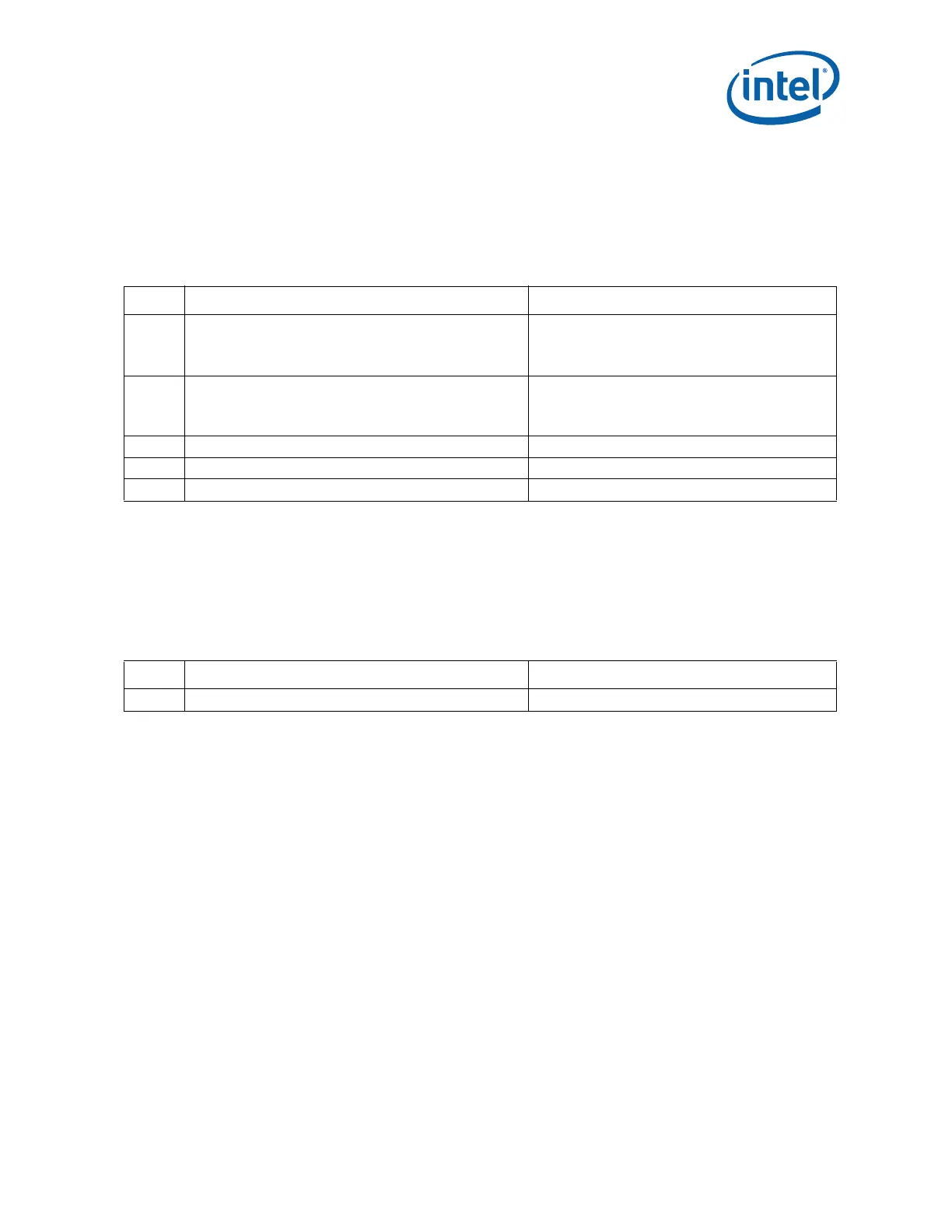

A.22 PCHSTRP20—Strap 20 Record (Flash Descriptor

Records)

Flash Address: FPSBA + 050h Size: 32 bits

Default Flash Address: 150h

Recommended Value:

Bits Description Usage

31 SATA MPHY Power Control

0 = Set as SATA MPHY Power Control (SATAPC) - Default

1 = Enable SATA Port 1 PCIe Port 6 Lane 2 Mode

(SATAP1_PCIEP6L2_MODE)

This strap configures the default state of GPIO35/

SATAP1_PCIE6L2B_MODE/SATAPC.

30 USB3 MPHY Power Control

0 = Set as USB3 MPHY Power Control (USB3PC) - Default

1 = Set as GPIO76

This strap configures the default state of GPIO76/

BMBUSYB/USB3PC. If it is not set as USB3PC, the pin

will switch to GPIO (Input) until it is configured by SW

to BMBUSY#.

29:3 Reserved, set to ’0’

2 Reserved, set to ‘1’

1:0 Reserved, set to ’0’

Bits Description Usage

31:0 Reserved, set to ’0’

Loading...

Loading...