28 523462

Intel Confidential

Descriptor Overview

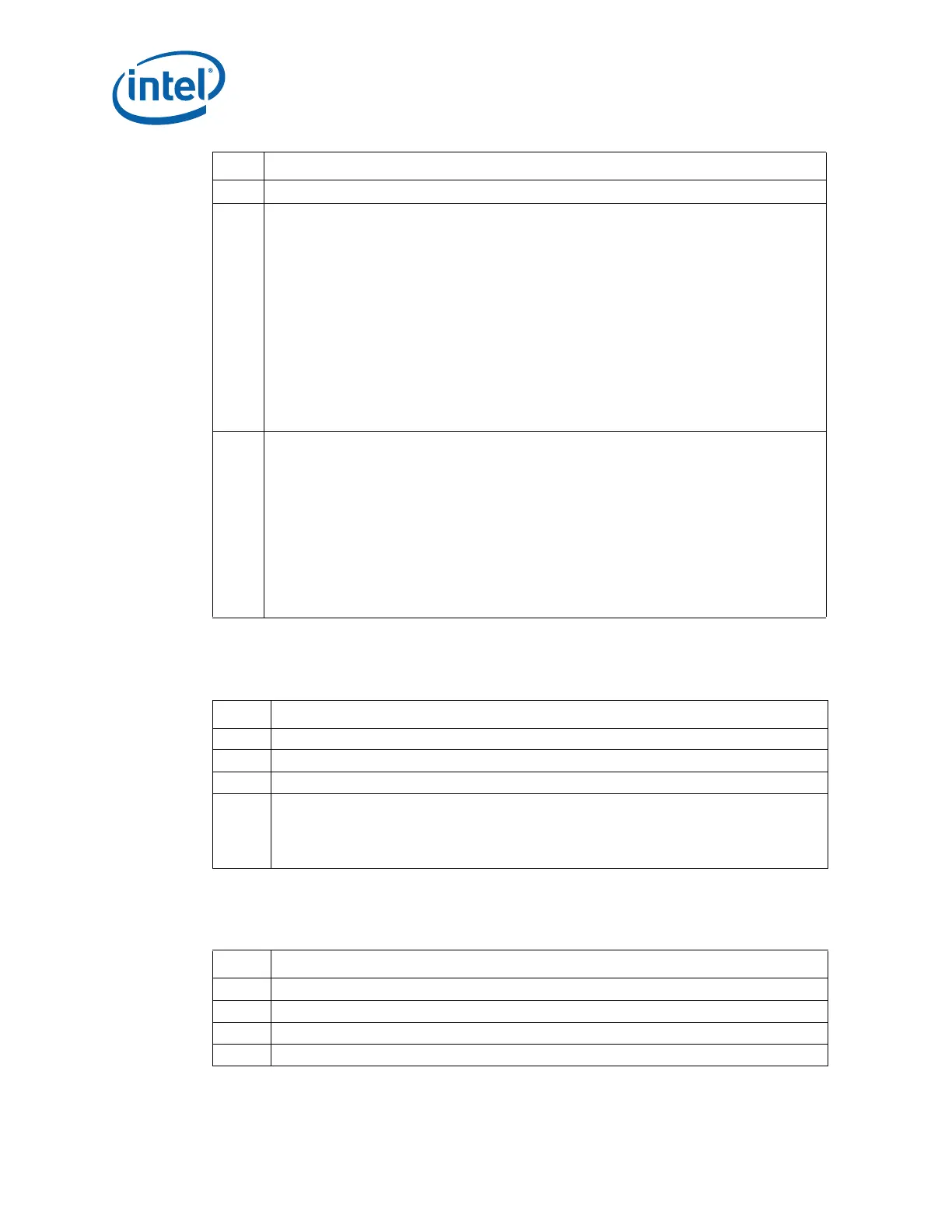

4.1.2.2 FLILL—Flash Invalid Instructions Register

(Flash Descriptor Records)

Memory Address: FCBA + 004h Size: 32 bits

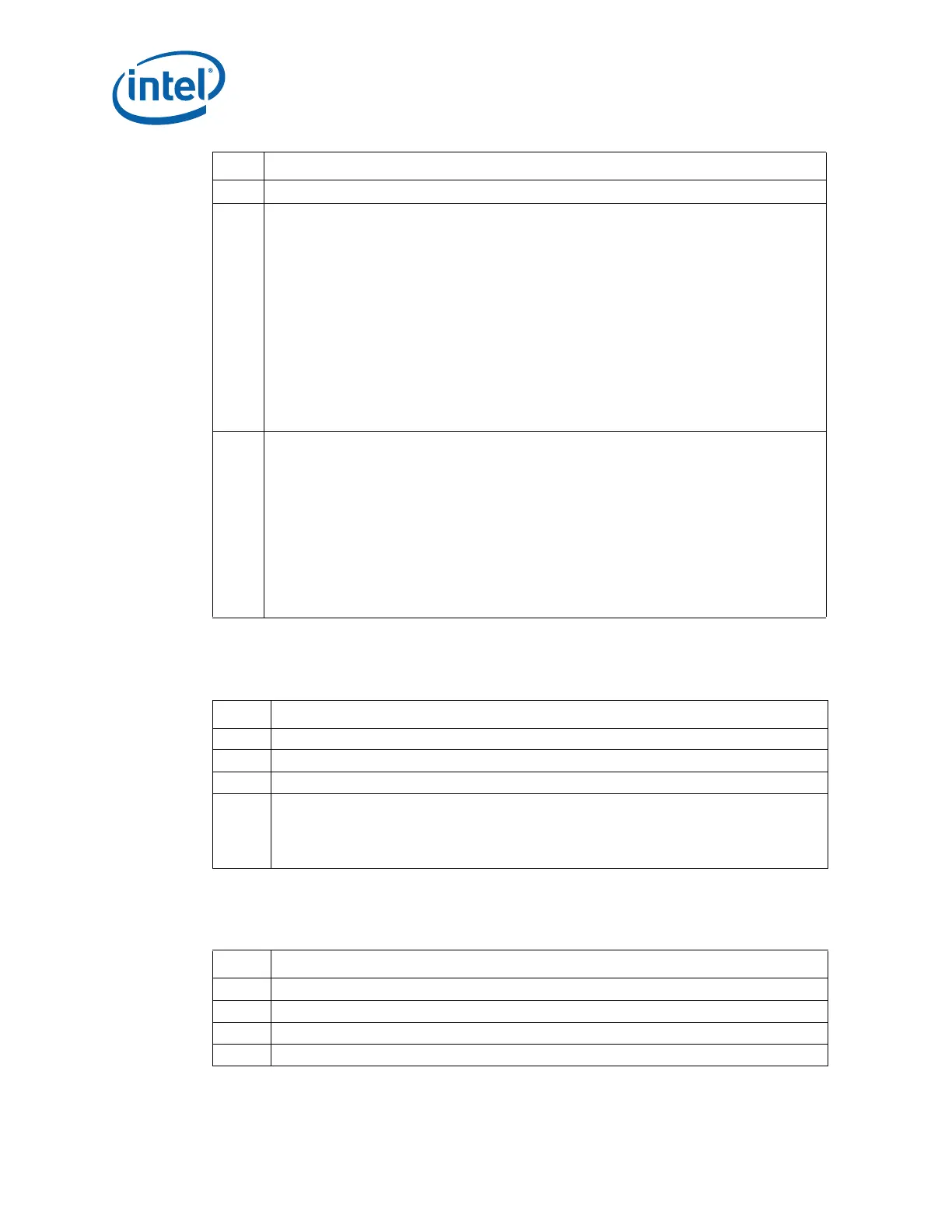

4.1.2.3 FLILL1—Flash Invalid Instructions Register

(Flash Descriptor Records)

Memory Address: FCBA + 008h Size: 32 bits

16:8

Reserved

7:4

Component 1 Density. (C1DEN) This field identifies the size of the 2nd Flash component

connected directly to the PCH. If there is not 2nd Flash component, the contents of this field should

be read as “1111b”

0000 = 512 KB

0001 = 1 MB

0010 = 2 MB

0011 = 4 MB

0100 = 8 MB

0101 = 16 MB

0110 = 32 MB

0111 = 64 MB

1000 - 1110 = Reserved

1111 = 2nd flash component not present

Note: This field is defaulted to “1111b” after reset

Note: C1DEN field will be ignored if FLMAP0.NC bit [9:8] is set to 00 i.e. 1 component only.

3:0

Component 0 Density (C0DEN). This field identifies the size of the 1st or only Flash component

connected directly to the PCH.

0000 = 512 KB

0001 = 1 MB

0010 = 2 MB

0011 = 4 MB

0100 = 8 MB

0101 = 16 MB

0110 = 32 MB

0111 = 64 MB

1000 - 1111 = Reserved

Note: This field is defaulted to “0101b” (16MB_) after reset.

Bits Description

Bits Description

31:24 Invalid Instruction 3. See definition of Invalid Instruction 0

23:16 Invalid Instruction 2. See definition of Invalid Instruction 0

15:8 Invalid Instruction 1. See definition of Invalid Instruction 0

7:0

Invalid Instruction 0.

Opcode for an instruction that the Flash Controller should protect against, such as Chip Erase. This

byte should be set to 0 if there are no invalid instructions to protect against for this field. Opcodes

programmed in the Software Sequencing Opcode Menu Configuration and Prefix-Opcode

Configuration are not allowed to use any of the Invalid Instructions listed in this register.

Bits Description

31:24 Invalid Instruction 7. See definition of Invalid Instruction 0

23:16 Invalid Instruction 6. See definition of Invalid Instruction 0

15:8 Invalid Instruction 5. See definition of Invalid Instruction 0

7:0 Invalid Instruction 4. See definition of Invalid Instruction 0

Loading...

Loading...