523462 31

Intel Confidential

Descriptor Overview

4.1.4 Flash Descriptor Master Section

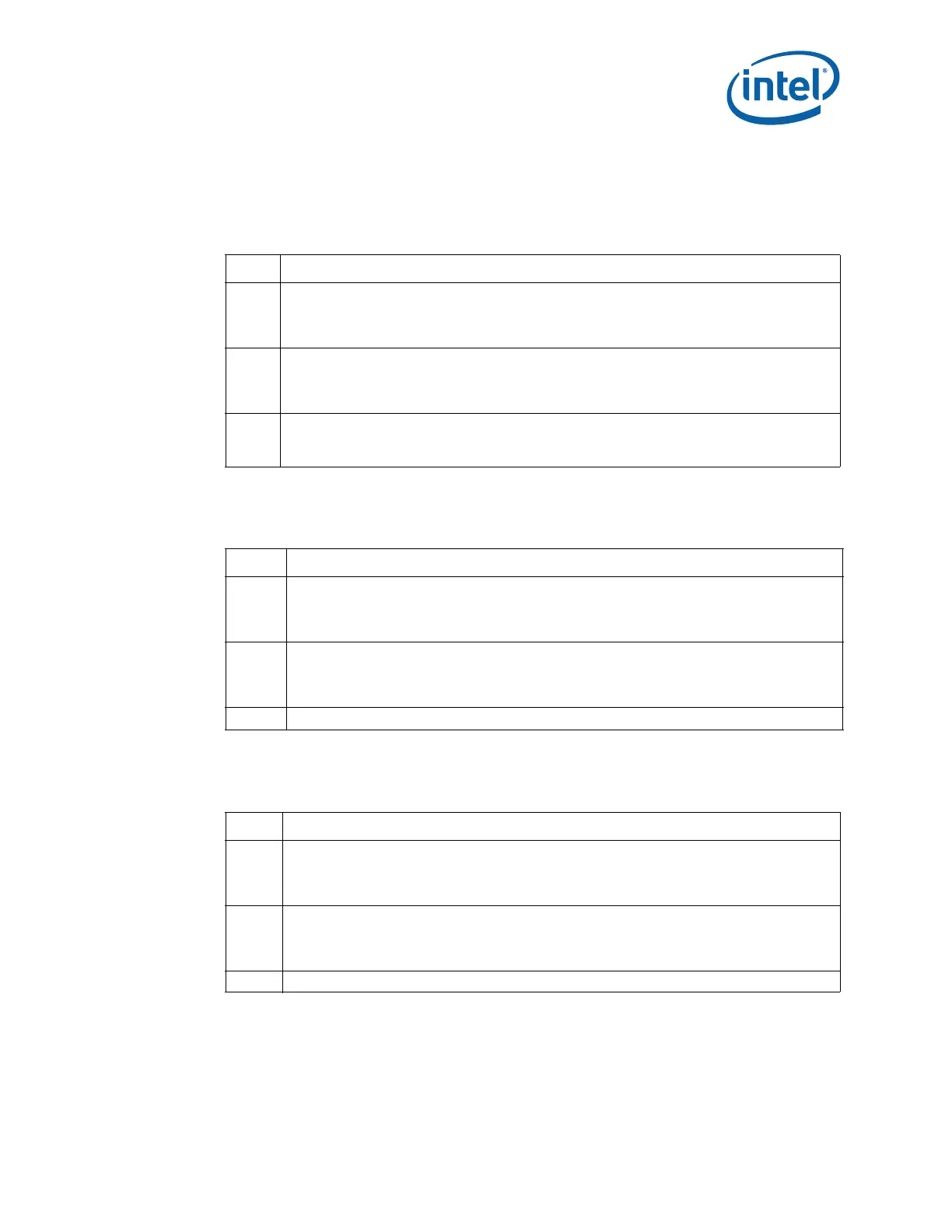

4.1.4.1 FLMSTR1—Flash Master 1 (Host CPU/ BIOS)

(Flash Descriptor Records)

Memory Address: FMBA + 000h Size: 32 bits

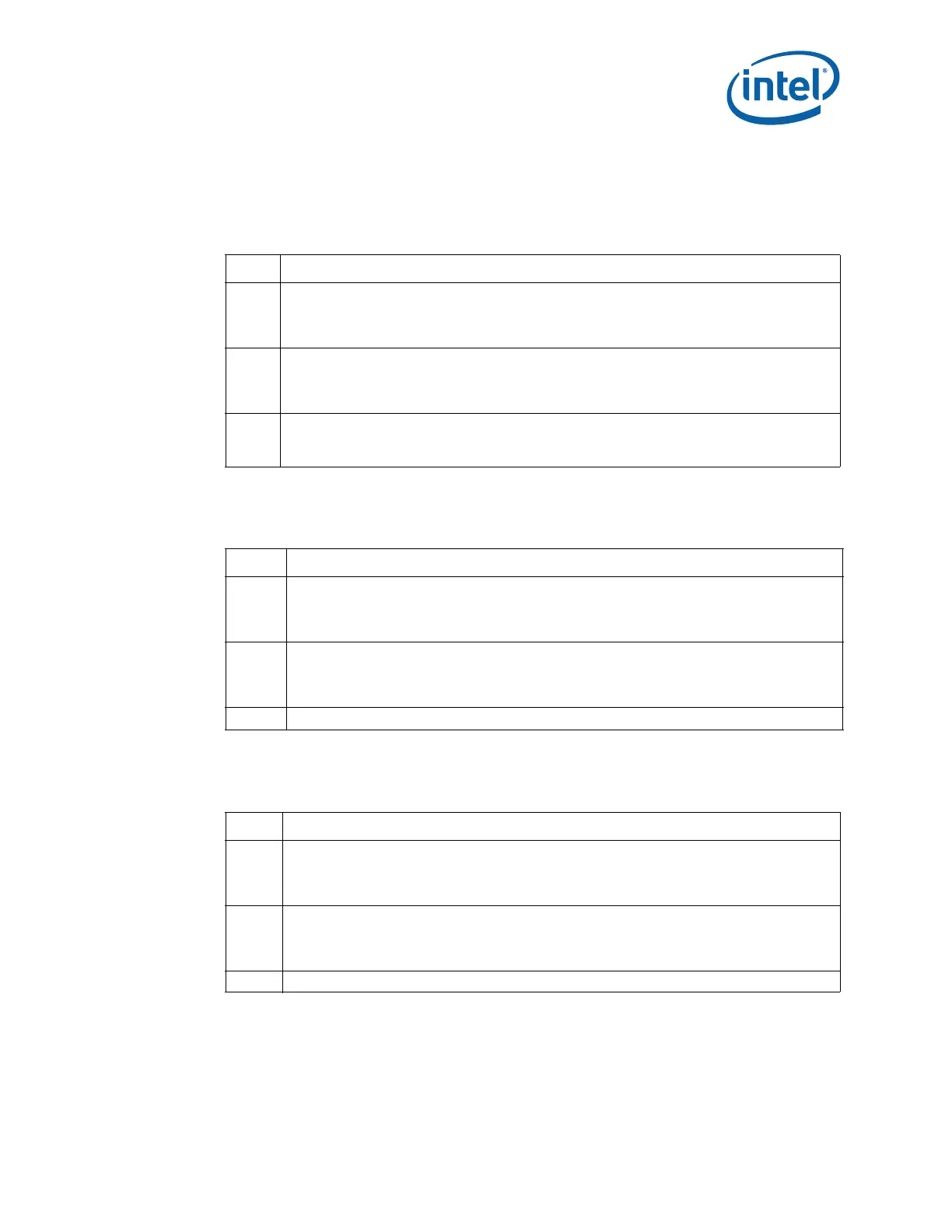

4.1.4.2 FLMSTR2—Flash Master 2 (Intel

®

ME)

(Flash Descriptor Records)

Memory Address: FMBA + 004h Size:32 bits

4.1.4.3 FLMSTR3—Flash Master 3 (GbE)

(Flash Descriptor Records)

Memory Address: FMBA + 008h Size:32 bits

Bits Description

31:24

Master Region Write Access: Each bit [31:24] corresponds to Regions [7:0]. If the bit is set, this

master can erase and write that particular region through register accesses.

Bit 23 is a don’t care as the primary master always has read/write permission to it’s primary region

23:16

Master Region Read Access: Each bit [23:16] corresponds to Regions [7:0]. If the bit is set, this

master can read that particular region through register accesses.

Bit 17 is a don’t care as the primary master always read/write permission to it’s primary region.

15:0

Requester ID: This is the Requester ID (Bus/Device/Function Number_ of the Host CPU

For the host CPU, this should be set to Bus/Device/Function: 0/0/0

Bits Description

31:24

Master Region Write Access: Each bit [31:24] corresponds to Regions [7:0]. If the bit is set, this

master can erase and write that particular region through register accesses.

Bit 26 is a don’t care as the primary master always has read/write permission to it’s primary region

23:16

Master Region Read Access: Each bit [23:16] corresponds to Regions [7:0]. If the bit is set, this

master can read that particular region through register accesses.

Bit 18 is a don’t care as the primary master always read/write permission to it’s primary region.

15:0 Requester ID: This is the Requester ID (Bus/Device/Function Number_ of the ME

Bits Description

31:24

Master Region Write Access: Each bit [31:24] corresponds to Regions [7:0]. If the bit is set, this

master can erase and write that particular region through register accesses.

Bit 27 is a don’t care as the primary master always has read/write permission to it’s primary region

23:16

Master Region Read Access: Each bit [23:16] corresponds to Regions [7:0]. If the bit is set, this

master can read that particular region through register accesses.

Bit 19 is a don’t care as the primary master always read/write permission to it’s primary region.

15:0 Requester ID: This is the Requester ID (Bus/Device/Function Number_ of the GbE

Loading...

Loading...