18 523462

Intel Confidential

PCH SPI Flash Compatibility Requirement

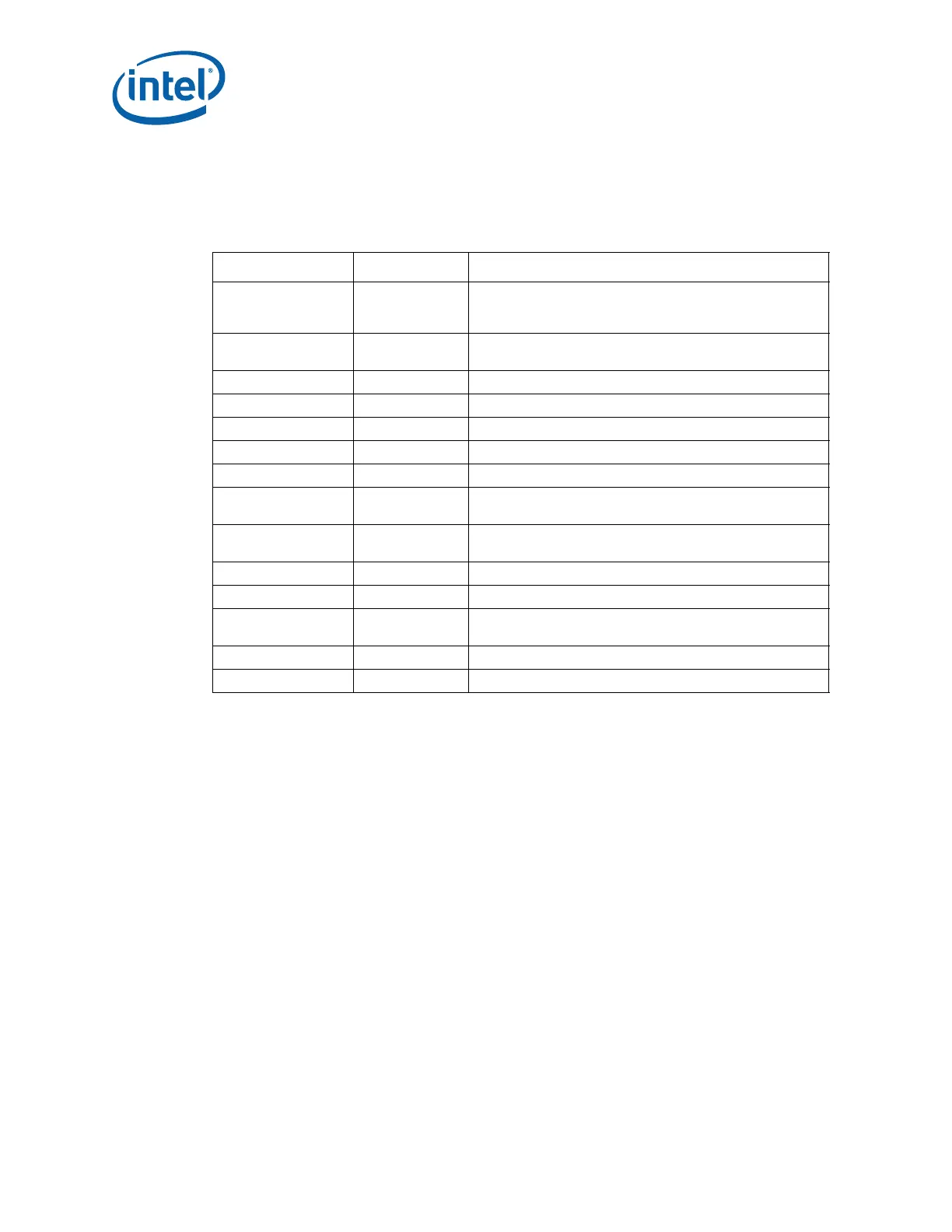

3.1.7 Hardware Sequencing Requirements

The following table contains a list of commands and the associated opcodes that a SPI-

based serial flash device must support in order to be compatible with hardware

sequencing.

Commands OPCODE Notes

Write to Status

Register

01h Writes a byte to SPI flash’s status register. Enable Write

to Status Register command must be run prior to this

command

Program Data 02h Single byte or 64 byte write as determined by flash part

capabilities and software

Read Data 03h

Write Disable 04h

Read Status 05h Outputs contents of SPI flash’s status register

Write Enable 06h

Fast Read 0Bh

Enable Write to

Status Register

50h or 06h Enables a bit in the status register to allow an update to

the status register

Erase Programmable/

Discoverable

4 Kbyte erase. Uses the value from SFDP (if available)

else value from VSCCn Erase Opcode register value

Chip Erase C7h and/or 60

JEDEC ID 9Fh See Section 3.1.5 for more information

Dual Output Fast

Read

3Bh/

Discoverable

Discoverable opcodes are obtained from each

component’s SFDP table

Dual I/O Fast Read Discoverable Opcode is optained from each component’s SFDP table

Quad I/O Fast Read Discoverable Opcode is optained from each component’s SFDP table

Loading...

Loading...