523462 85

Intel Confidential

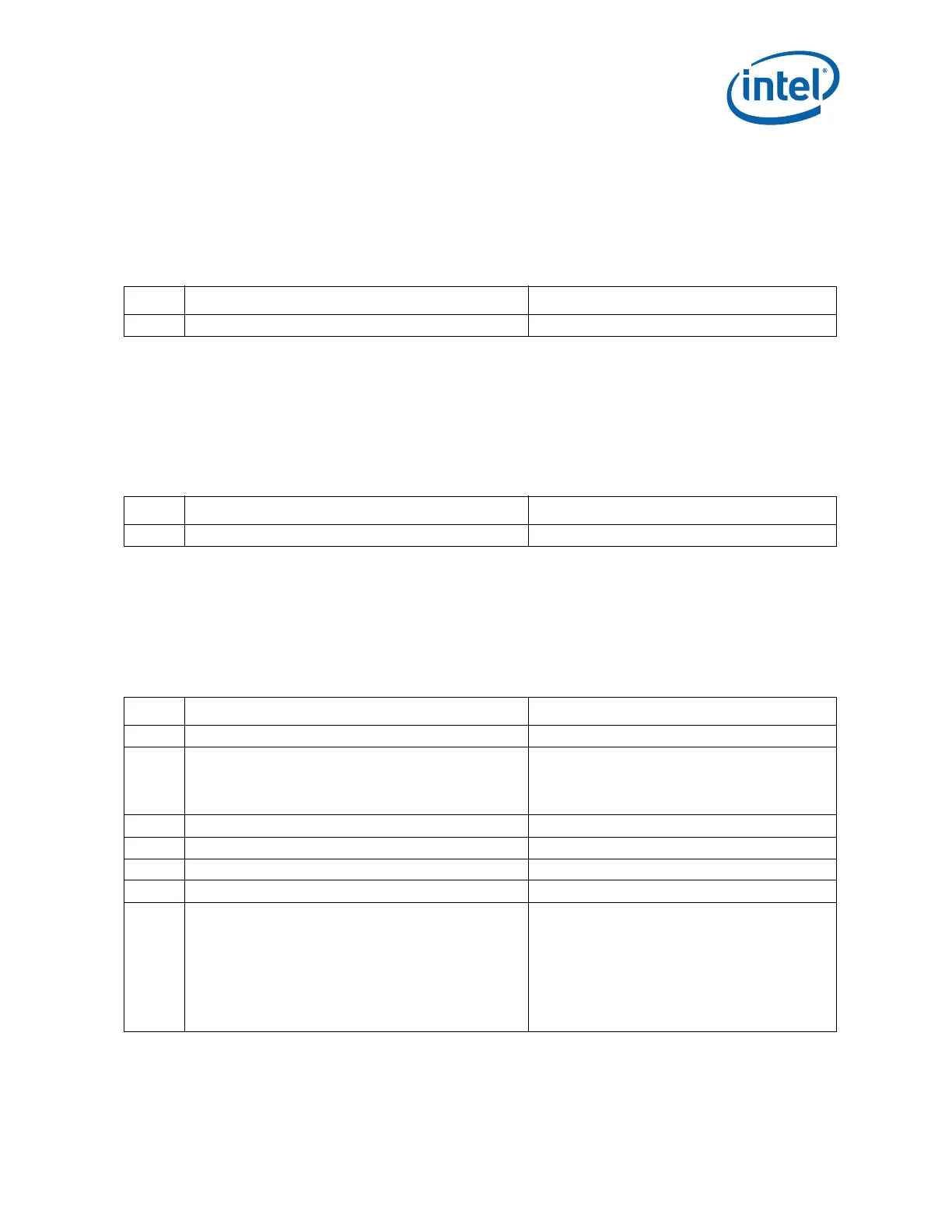

APPENDIX A - Descriptor Configuration

A.14 PCHSTRP12—Strap 12 Record (Flash Descriptor

Records)

Flash Address: FPSBA + 030h Default Value: 00000000h

Size: 32 bits

Default Flash Address: 130h

A.15 PCHSTRP13—Strap 13 Record (Flash Descriptor

Records)

Flash Address: FPSBA + 034h Default Value: 00000000h

Size: 32 bits

Default Flash Address: 134h

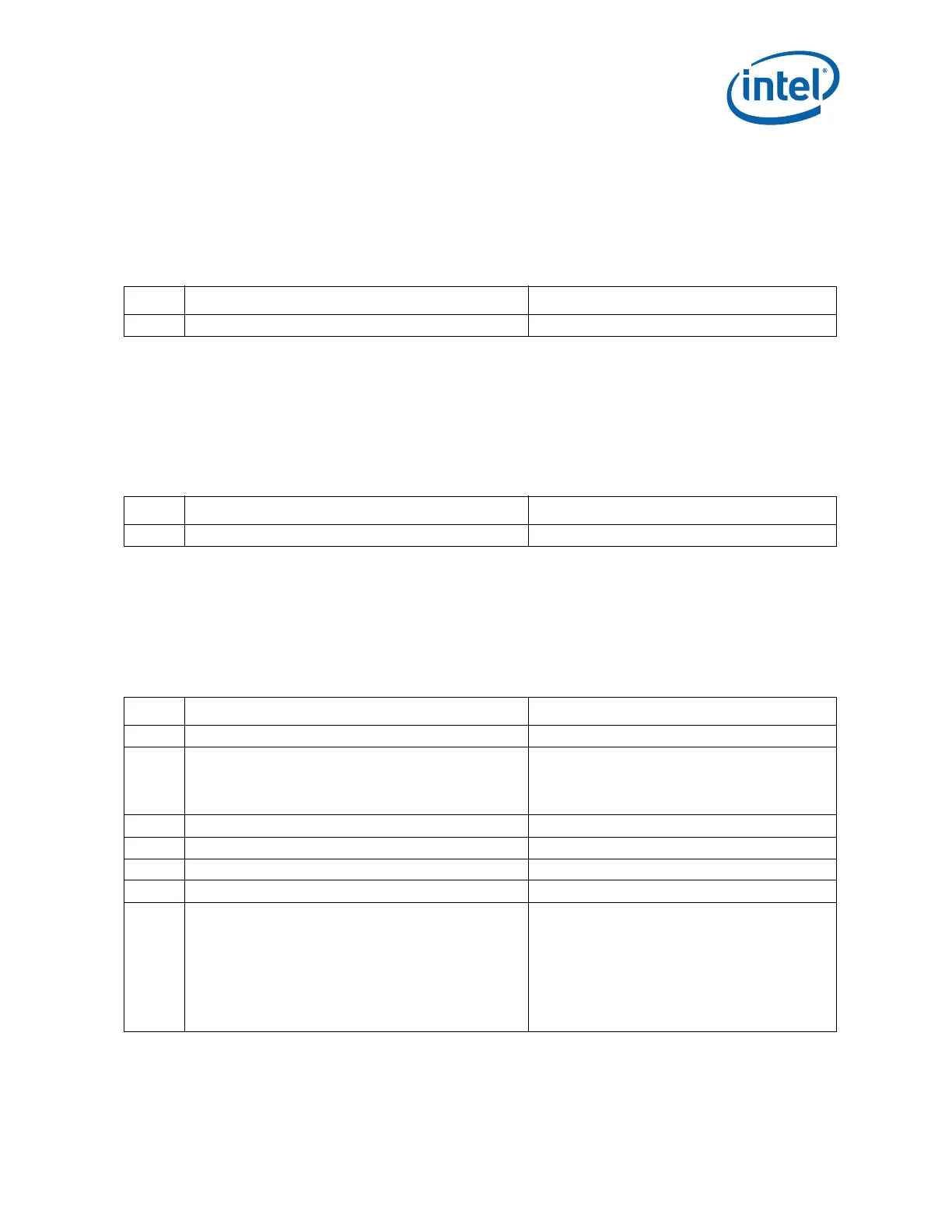

A.16 PCHSTRP14—Strap 14 Record (Flash Descriptor

Records)

Flash Address: FPSBA + 038h Default Value: 00000000h

Size: 32 bits

Default Flash Address: 138h

Bits Description Usage

31:0 Reserved, set to ’0’

Bits Description Usage

31:0 Reserved, set to ’0’

Bits Description Usage

31 Reserved, set to ’0’

30 SMLink1 / GPIO Select

0 – Pins assigned to GPIO [GPIO74 / GPIO75]

1 – Pins assigned to Native mode [SML1Data / SML1Clk]

This setting determines if the GPIO74 and GPIO75

pins are assigned to Native mode or assigned to

GPIO.

29:27 Chipset configuration, set to ‘011b’

26:23 Chipset configuration, set to ‘0010b’

22:19 Chipset configuration, set to ‘0101b’

18:15 Chipset configuration, set to ‘0100b’

14 PCIe Lane Reversal 3 (PCIELR3)

This bit lane reversal behavior for PCIe Port 6 if configured

as a x4 PCIe port.

0 = PCIe Lanes 0-3 are not reversed.

1 = PCIe Lanes 0-3 are reversed when Port 6 is configured

as a 1x4.

Note: This field only is in effect if PCIEPCS3 is set to '11'b.

If configuring PCIe* port 6 as a x4 PCIe bus,

reversing the lanes of this port is done via this strap.

PCI Express port lane reversal can be done to aid in

the laying out of the board.

Note: This setting is dependent on the board

design. The platform hardware designer must

determine if this port needs lane reversal.

Loading...

Loading...