523462 83

Intel Confidential

APPENDIX A - Descriptor Configuration

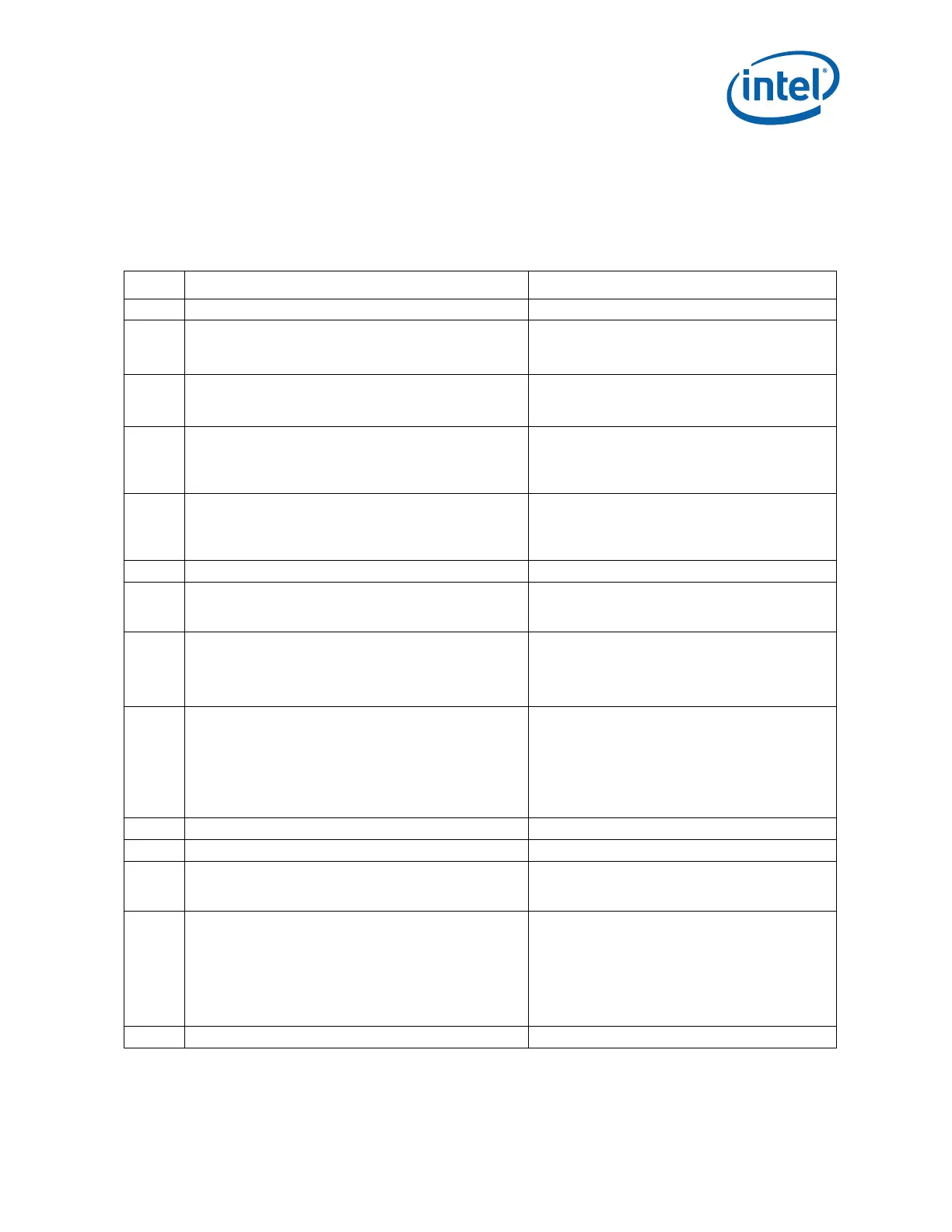

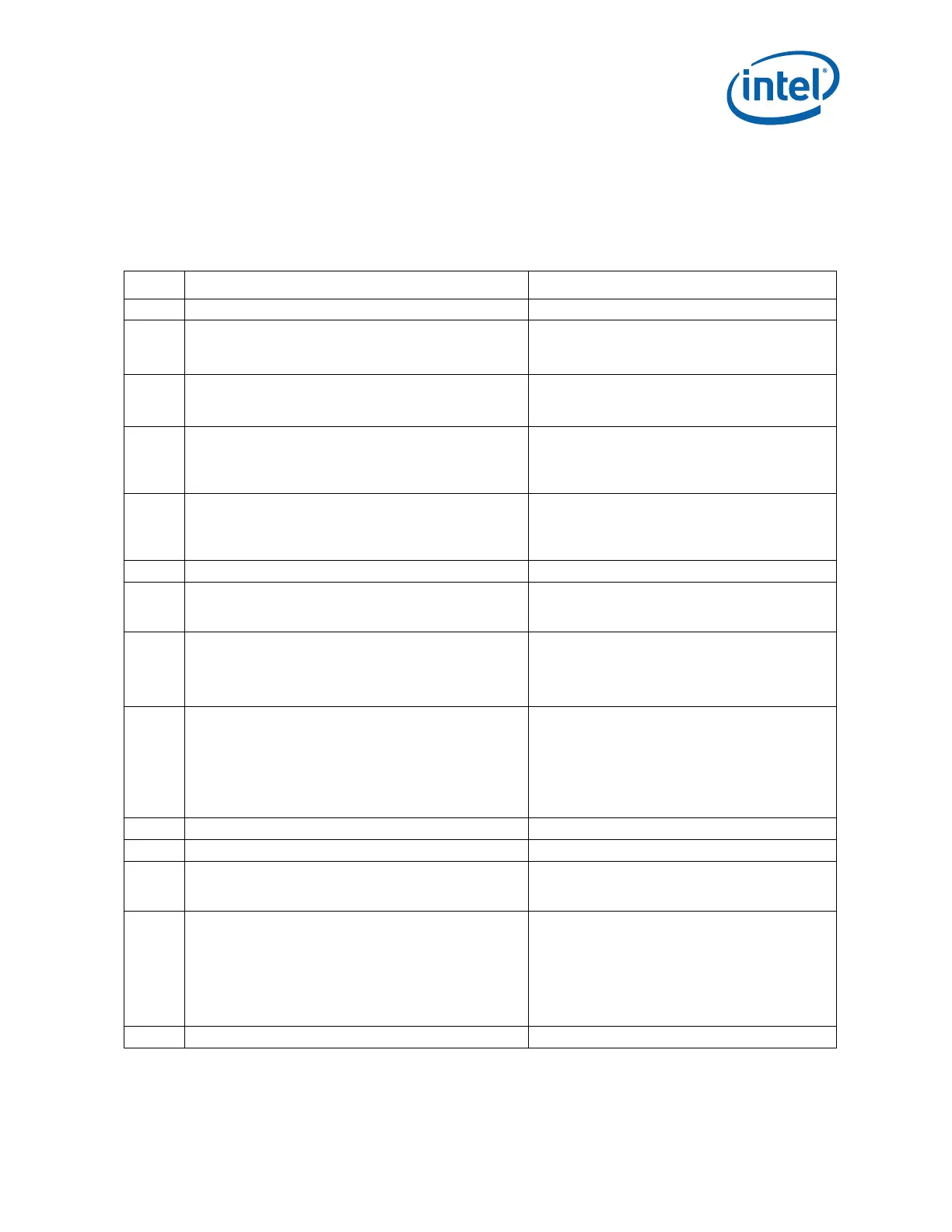

A.12 PCHSTRP10—Strap 10 Record (Flash Descriptor

Records)

Flash Address: FPSBA + 028h Size: 32 bits

Default Flash Address: 128h

Bits Description Usage

31:25 Reserved set to ‘0’

24

Intel

®

ME Debug LAN Emergency Mode

0 = Intel ME LAN Debug Disable

1 = Enables Emergency mode of Intel ME LAN Debug mode

Note: Default for production platforms should be ‘0’

23

Deep SX Support (Deep_SX_EN)

0 = Deep SX NOT supported on the platform

1 = Deep SX supported on the platform

This requires the target platform to support Deep SX

state

22

Integrated Clocking Controller (ICC) Profile Selection

(ICC_PRO_SEL)

0 = ICC Profile will be provided by BIOS

1 = ICC Profile selected by Softstraps (ICC_SEL)

21

Intel

®

ME Reset Capture on CL_RST1#: (MER_CL1)

0 = PCH Signal CL_RST1# does NOT assert when Intel ME

performs a reset.

1 = PCH Signal CL_RST1# asserts when Intel ME resets.

Notes: Signal CL_RST1# is only present on mobile

PCH

20:17 Reserved set to ‘0’

16 ME Debug Extended Data Enable

0 = Enable

1 = Disable

15:9

ME Debug SMBus Emergency Mode Address

(MDSMBE_ADD):

SMBUS address used for ME Debug status writes. If this field

is 00h, the default address, 38h, is used.

Note: Please set this field 00h by default.

This field is only used for testing purposes.

8

ME Debug SMBus Emergency Mode Enable

(MDSMBE_EN):

0 = Disable Intel ME Debug status writes

1 = Enable Intel ME Debug status writes over SMBUS using

the address set by MMADDR.

This field is only used for testing purposes.

When this bit is enabled, you will see writes on SMBus

to address 38h

bits address (70h bit shifted), or value is specified in

MDSMBE_ADD.

MDSMBE_ADD specifies address bits [7:1] of the

target address.

7 Reserved

6:3 Reserved, set to ’0’

2

Intel

®

Platform Trusted Technology (PTT) Disable

0 = PTT enabled

1 = PTT disabled

1 ME Boot Flash (ME_Boot_Flash).

0 = Intel Management Engine will boot from ROM, then

flash

1 = Intel Management Engine will boot from flash

Note: This field should only be set to ’1b’ if the Intel ME

binary loaded in the platform has a ME ROM Bypass

image

This bit must be set to 0 for production PCH based

platforms.

This bit will only be set to ’1’ in order to work around

issues in pre-production hardware and Intel ME FW.

0 Reserved, Default set to ’0’

Loading...

Loading...