32 523462

Intel Confidential

Descriptor Overview

4.1.5 PCH Softstraps

See Appendix A for Record descriptions and listings.

4.1.6 Descriptor Upper Map Section

4.1.6.1 FLUMAP1—Flash Upper Map 1

(Flash Descriptor Records)

Memory Address:FDBAR + EFCh Size: 32 bits

4.1.7 Intel

®

ME Vendor Specific Component Capabilities Table

Entries in this table allow support for a SPI flash part for Intel Management Engine

capabilities including Intel

®

Active Management Technology.

Since Flash Partition Boundary Address (FPBA) has been removed, UVSCC and LVSCC

has been replaced with VSCC0 and VSCC1 in Broadwell PCH-LP. VSCC0 is for SPI

component 0 and VSCC1 is for SPI component 1.

If SFDP tables are not found by the SPI controller, then the VSCCn must be written

before Intel ME can issue a Write or Erase command using the Intel ME Hardware

Sequencing interface. BIOS will still need to set up the proper VSCC registers for BIOS

and Integrated Gigabit Ethernet usage if there is no SFDP table found.

Each VSCC table entry is composed of two 32 bit fields: JEDEC IDn and the

corresponding VSCCn value.

See 4.4 Intel

®

ME Vendor-Specific Component Capabilities (Intel

®

ME VSCC) Table for

information on how to program individual entries.

4.1.7.1 JID0—JEDEC-ID 0 Register

(Flash Descriptor Records)

Memory Address: VTBA + 000h Size: 32 bits

4.1.7.2 VSCC0—Vendor Specific Component Capabilities 0

(Flash Descriptor Records)

Memory Address: VTBA + 004h Size: 32 bits

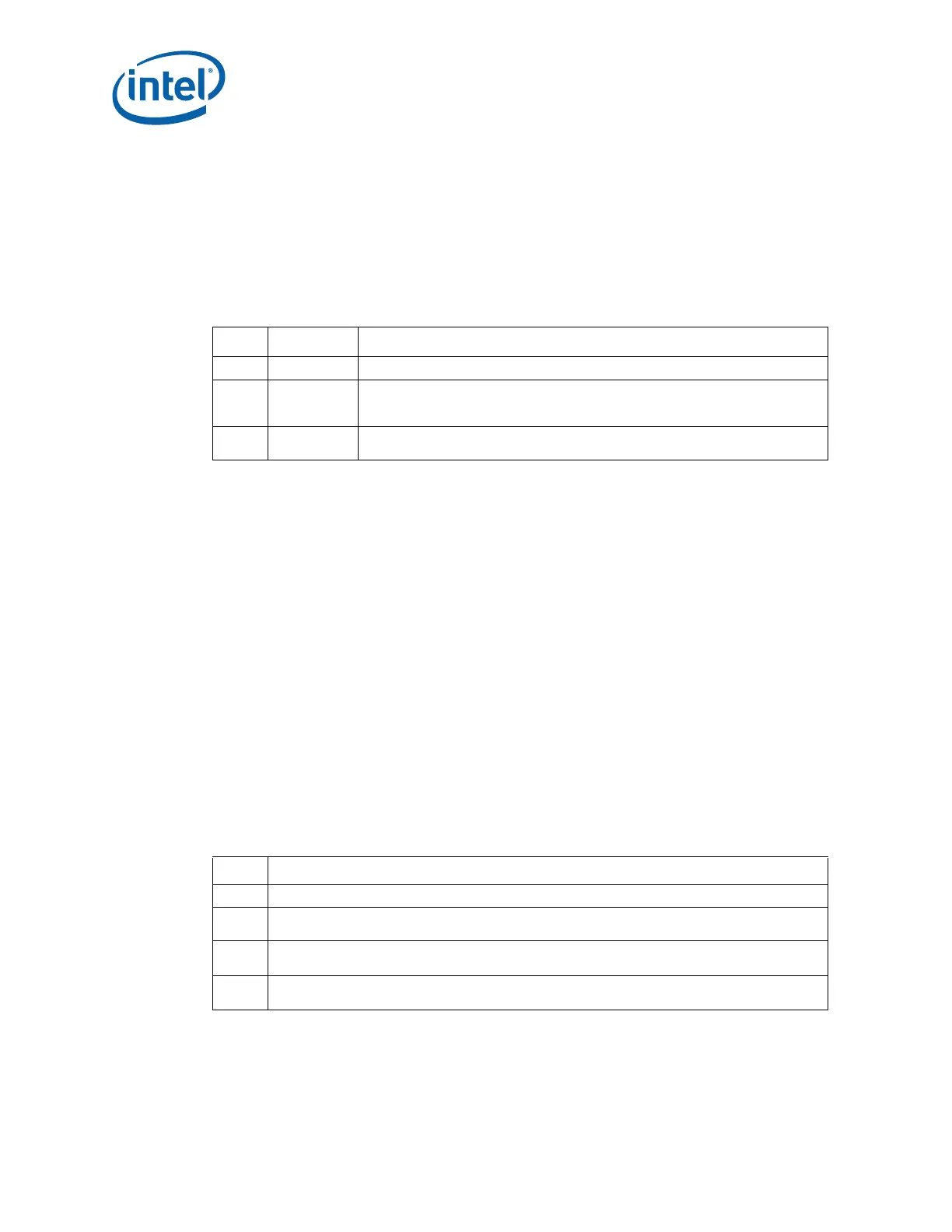

Bits Default Description

31:16 0

Reserved

15:8 1

Intel

®

ME VSCC Table Length (VTL). Identifies the 1s based number of

DWORDS contained in the VSCC Table. Each SPI component entry in the table is 2

DWORDS long.

7:0 1

Intel

®

ME VSCC Table Base Address (VTBA). This identifies address bits [11:4]

for the VSCC Table portion of the Flash Descriptor. Bits [26:12] and bits [3:0] are 0.

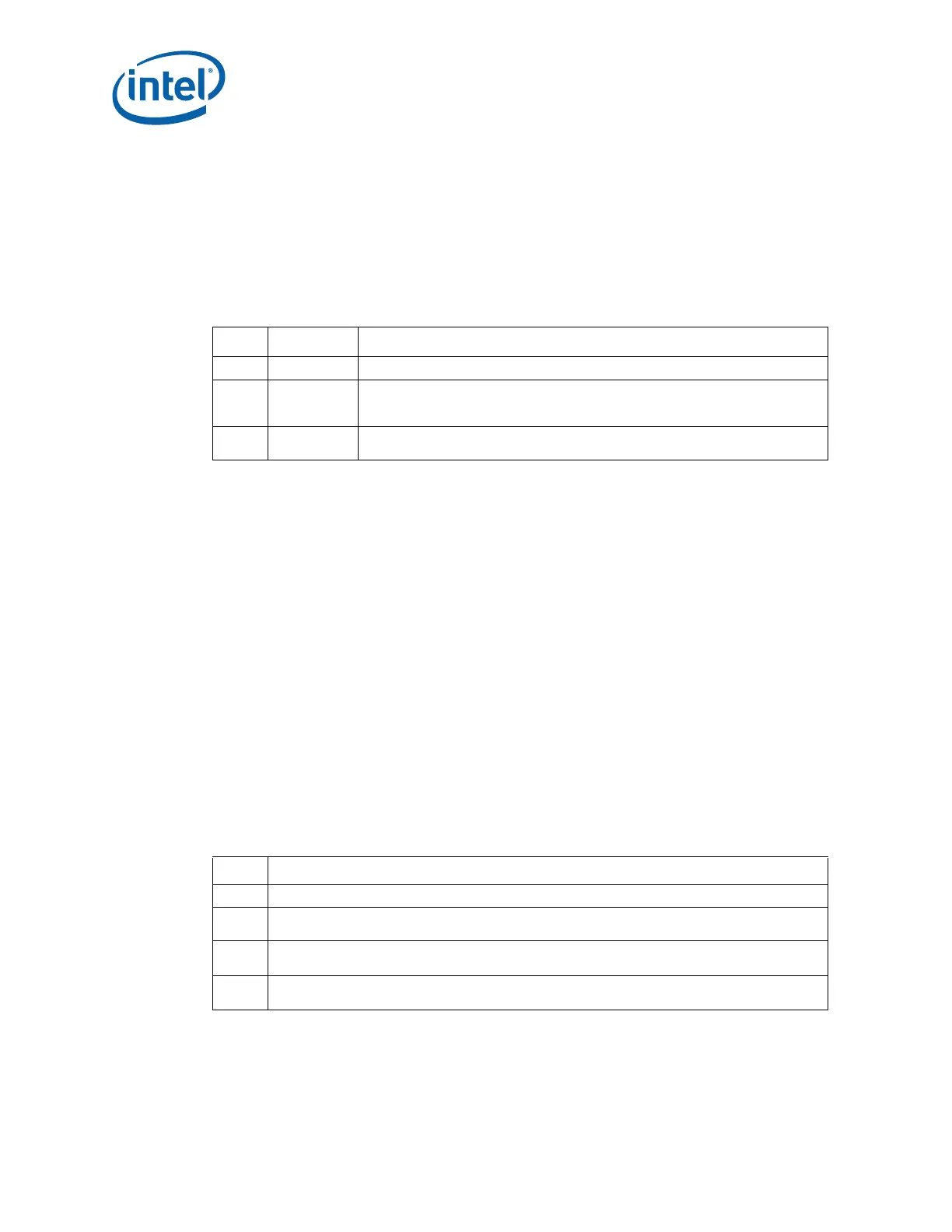

Bits Description

31:24 Reserved

23:16

SPI Component Device ID 1. This field identifies the second byte of the Device ID of the SPI Flash

Component. This is the third byte returned by the Read JEDEC-ID command (opcode 9Fh).

15:8

SPI Component Device ID 0. This field identifies the first byte of the Device ID of the SPI Flash

Component. This is the second byte returned by the Read JEDEC-ID command (opcode 9Fh).

7:0

SPI Component Vendor ID. This field identifies the one byte Vendor ID of the SPI Flash

Component. This is the first byte returned by the Read JEDEC-ID command (opcode 9Fh).

Loading...

Loading...