84 523462

Intel Confidential

APPENDIX A - Descriptor Configuration

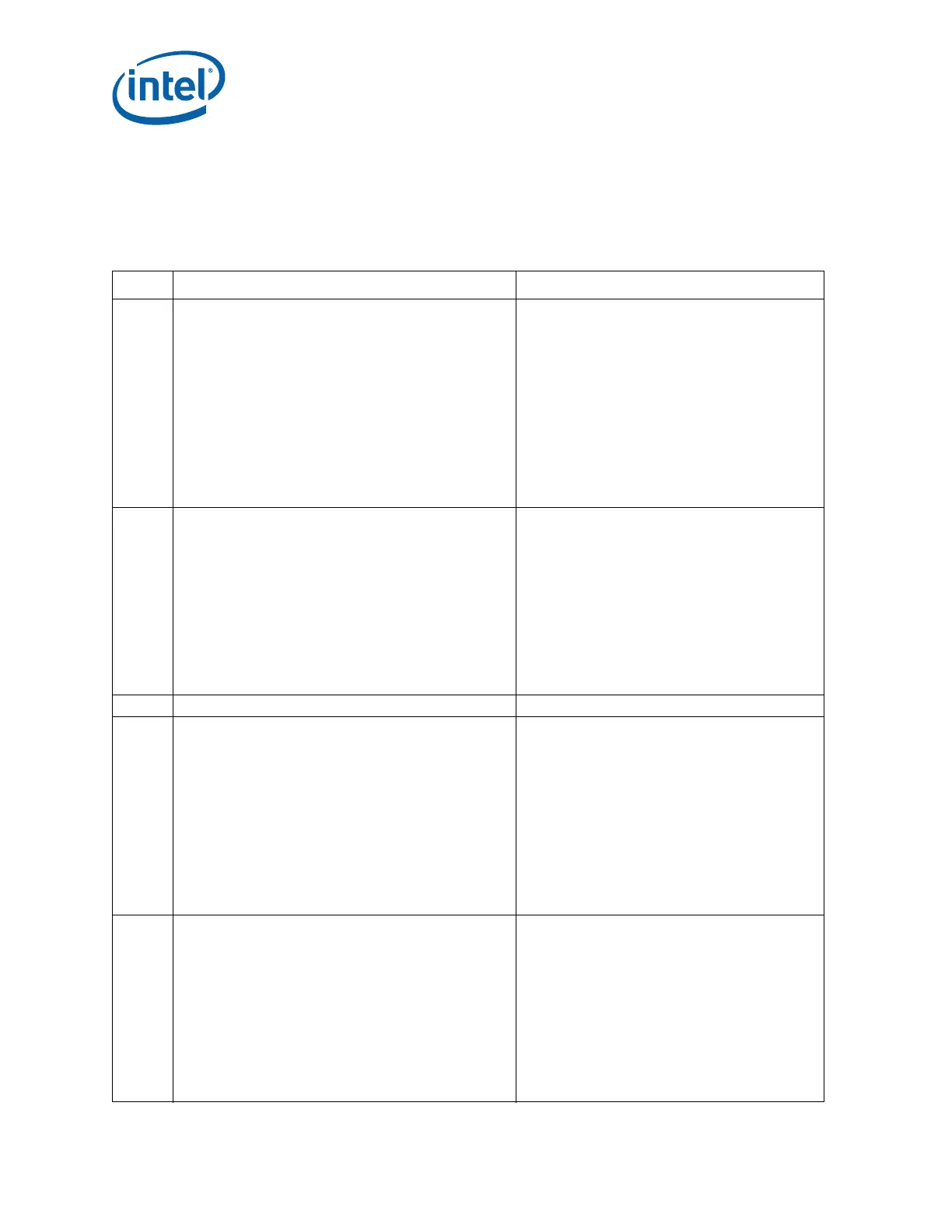

A.13 PCHSTRP11—Strap 11 Record (Flash Descriptor

Records)

Flash Address: FPSBA + 02Ch Size: 32 bits

Default Flash Address: 12Ch

Bits Description Usage

31:25

SMLink1 I

2

C* Target Address (SML1I2CA)

Defines the 7 bit I2C target address for PCH Thermal

Reporting on SMLink1.

Notes:

1. This field is not active unless SML1I2CAEN is set to ’1’.

2. This address MUST be set if there is a device on the

SMLink1 segment that will use thermal reporting

supplied by PCH.

3. If SML1I2CAEN =’1’ then this field must be a valid 7

bit, non-zero address that does not conflict with any

other devices on SMLink1 segment.

4. This address can be different for every design, ensure

BIOS developer supplies the address.

When SML1I2CAEN(PCHSTRP11 bit 24) =’1’,

there needs to be a valid I

2

C address in this field. This

address used here is design specific. The BIOS

developer and/or platform hardware designer must

supply an address with the criteria below.

A valid address must be:

•Non-zero value

• Must be a unique address on the SMLink1

segment

• Be compatible with the master on SMLink1 - For

example, if the I

2

C address the master that

needs write thermal information to a address

"xy"h. Then this filed must be to "xy"h.

24

SMLink1 I

2

C Target Address Enable (SML1I2CAEN)

0 = SMLink1 I

2

C Address is disabled

1 = SMLink1 I

2

C Address is enabled

Notes:

1. This bit MUST set to ’1’ if there is a device on the

SMLink1 segment that will use PCH thermal reporting.

2. This bit MUST be set to ’0’ if PCH thermal reporting is

not used.

This bit must be set in cases where SMLink1 has a

master that requires SMBus based Thermal Reporting

that is supplied by the PCH. Some examples of this

master could be an Embedded Controller, a BMC, or

any other SMBus Capable device that needs Processor

and/or PCH temperature information. If no master on

the SMLink1 segment is capable of utilizing thermal

reporting, then this field must be set to ’0’.

Note: This setting is not the same for all designs, is

dependent on the board design. The setting

of this field must be determined by the BIOS

developer and the platform hardware

designer.

23:8 Reserved, set to ’0’

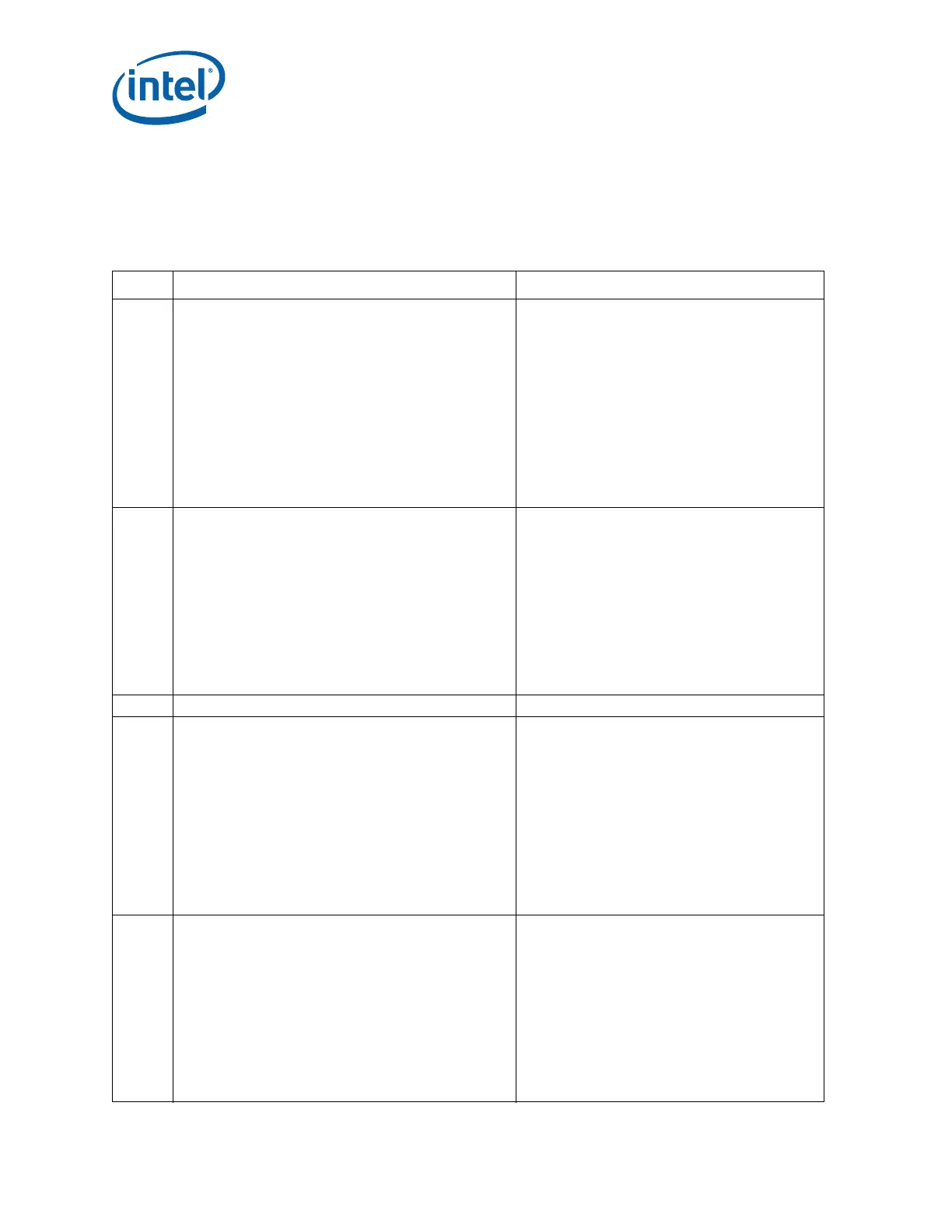

7:1

SMLink1 GP Address (SML1GPA):

SMLink1 controller General Purpose Target Address (7:1)

Notes:

1. This field is not active unless SML1GPAEN is set to ’1’.

2. This address MUST be set if there is a device on the

SMLink1 segment that will use SMBus based PCH

thermal reporting.

3. If SML1GPAEN =’1’ then this field must be a valid 7

bit, non-zero address that does not conflict with any

other devices on SMLink1 segment.

When SML1GPAEN =’1’, there needs to be a valid GP

address in this field. This address used here is design

specific. The BIOS developer and/or platform

hardware designer must supply an address with the

criteria below.

A valid address must be:

• Non-zero value

• Must be a unique address on the SMLink1

segment

• Be compatible with the master on SMLink1 - For

example if the GP address the master that needs

read thermal information from a certain address,

then this filed must be set accordingly.

0

SMLink1 GP Address Enable(SML1GPAEN):

SMLink1 controller General Purpose Target Address Enable

0 = SMLink1 GP Address is disabled

1 = SMLink1 GP Address is enabled

Notes:

1. This bit MUST set to ’1’ if there is a device on the

SMLink1 segment that will use SMBus based PCH

thermal reporting.

2. This bit MUST be set to ’0’ if PCH thermal reporting is

not used.

This bit must be set in cases where SMLink1 has a

master that requires SMBus based Thermal Reporting

that is supplied by the PCH. Some examples of this

master could be an Embedded Controller, a BMC, or

any other SMBus Capable device that needs Processor

or PCH temperature information. If no master on the

SMLink1 segment is capable of utilizing thermal

reporting, then this field must be set to ’0’.

Note: This setting is not the same for all designs, is

dependent on the board design. The setting

of this field must be determined by the BIOS

developer and the platform hardware

designer.

Loading...

Loading...