73

ECP5 and ECP5-5G High-Speed I/O Interface

Soft IP Modules

The following soft IP Modules are available for use with the Generic DDR interfaces described above. All of the soft

IP Modules can be generated using Clarity Designer. Table 38 below summarizes the list of soft IPs available and

the ones that are optional vs the ones that will be automatically generated with the interface in Clarity Designer.

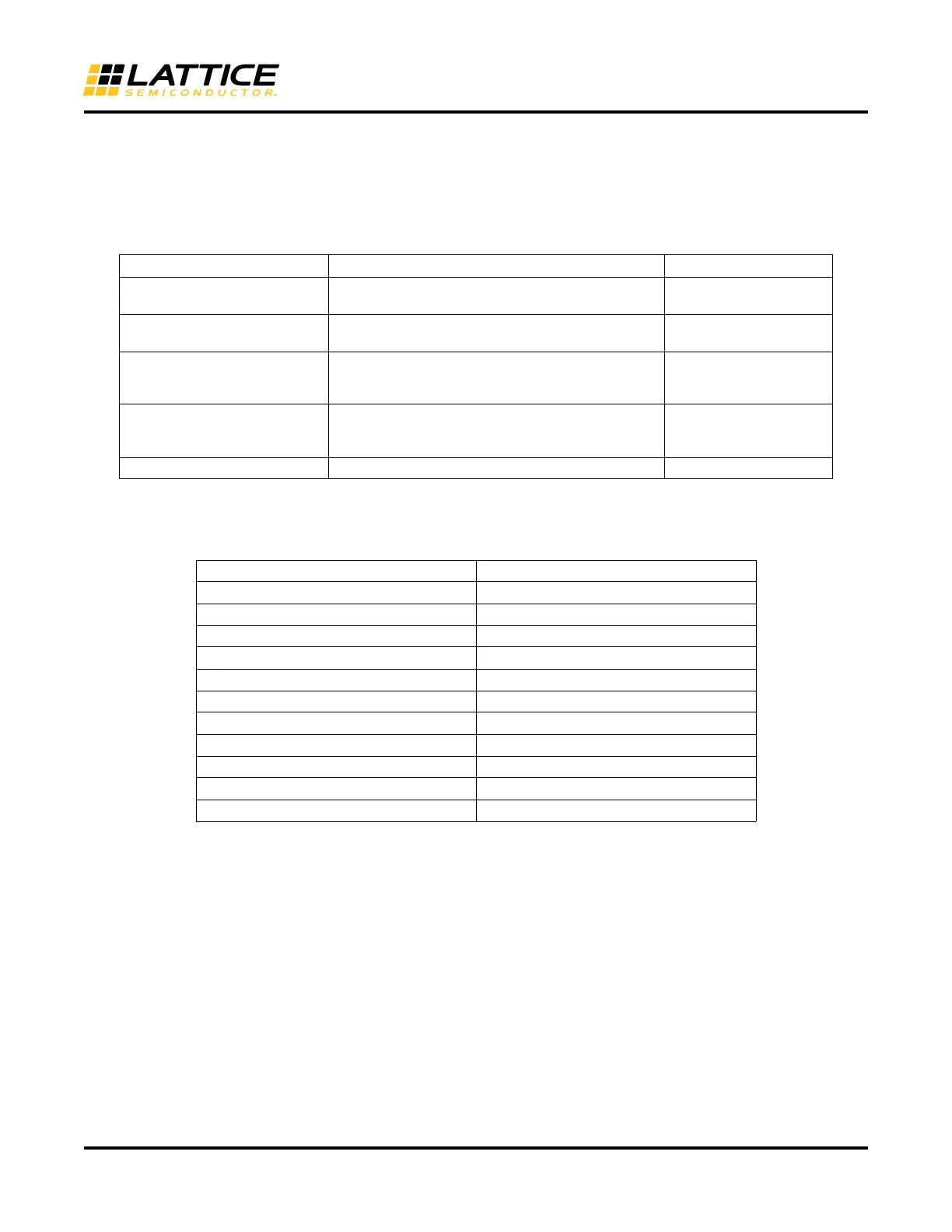

Table 38. List of Soft IPs supported

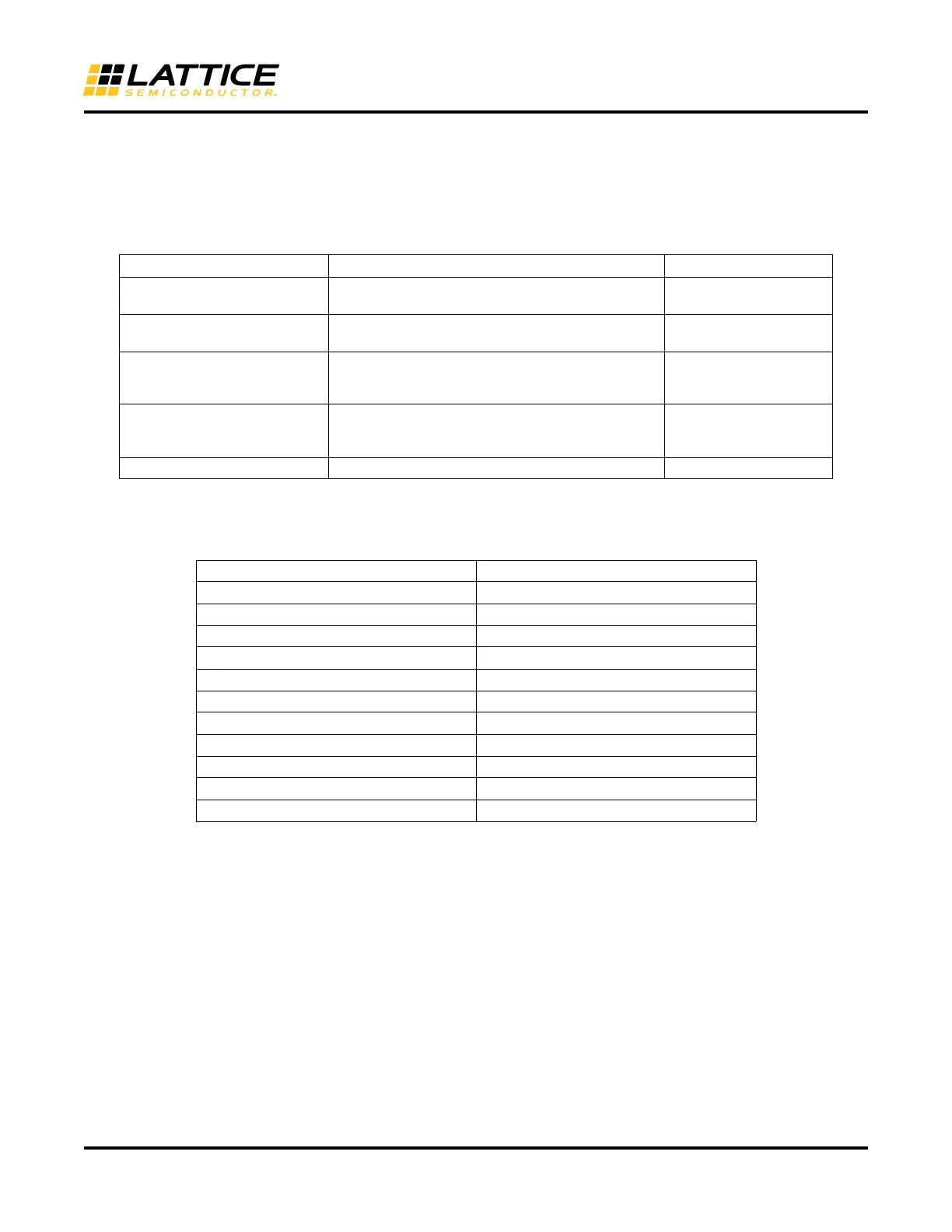

Table 39 below summarized the soft IPs used in each interface.

Table 39. Soft IP Used in Each Interface

Soft IP Name Function Required

RX_SYNC Used to break up the DDRDLL to DLLDEL clock loop

for Aligned Interfaces

Ye s

GDDR_SYNC Needed to tolerate large skew between stop and

reset input

Ye s

MEM_SYNC Needed to avoid issues on DDR memory bus and

update code in operation without interrupting inter-

face operation.

Ye s

7:1 LVDS Bit and Word Align-

ment (BW_ALIGN)

The soft IP is used to perform bit and word alignment

using PLL’s dynamic phase shift interface and aligned

input of IDDR71C.

Optional

MIPI_FILTER Implements low pass filter on low speed MIPI data Optional

Interface Soft IP

GDDRX1_RX.SCLK.Centered None

GDDRX1_RX.SCLK.Aligned RX_SYNC

GDDRX2_RX.ECLK.Centered GDDR_SYNC

GDDRX2_RX.ECLK.Aligned RX_SYNC

GDDRX2_RX.MIPI GDDR_SYNC, MIPI_FILTER

GDDRX71_RX.ECLK GDDR_SYNC, BW_ALIGN

GDDRX1_TX.SCLK.Centered None

GDDRX1_TX.SCLK.Aligned None

GDDRX2_TX.ECLK.Centered GDDR_SYNC

GDDRX2_TX.ECLK.Aligned GDDR_SYNC

GDDRX71_TX.ECLK GDDR_S

Loading...

Loading...