477

APPENDICES

A

Appendix 3 CPU Module Processing Time

Appendix 3.2 Time required for each processing included in scan time

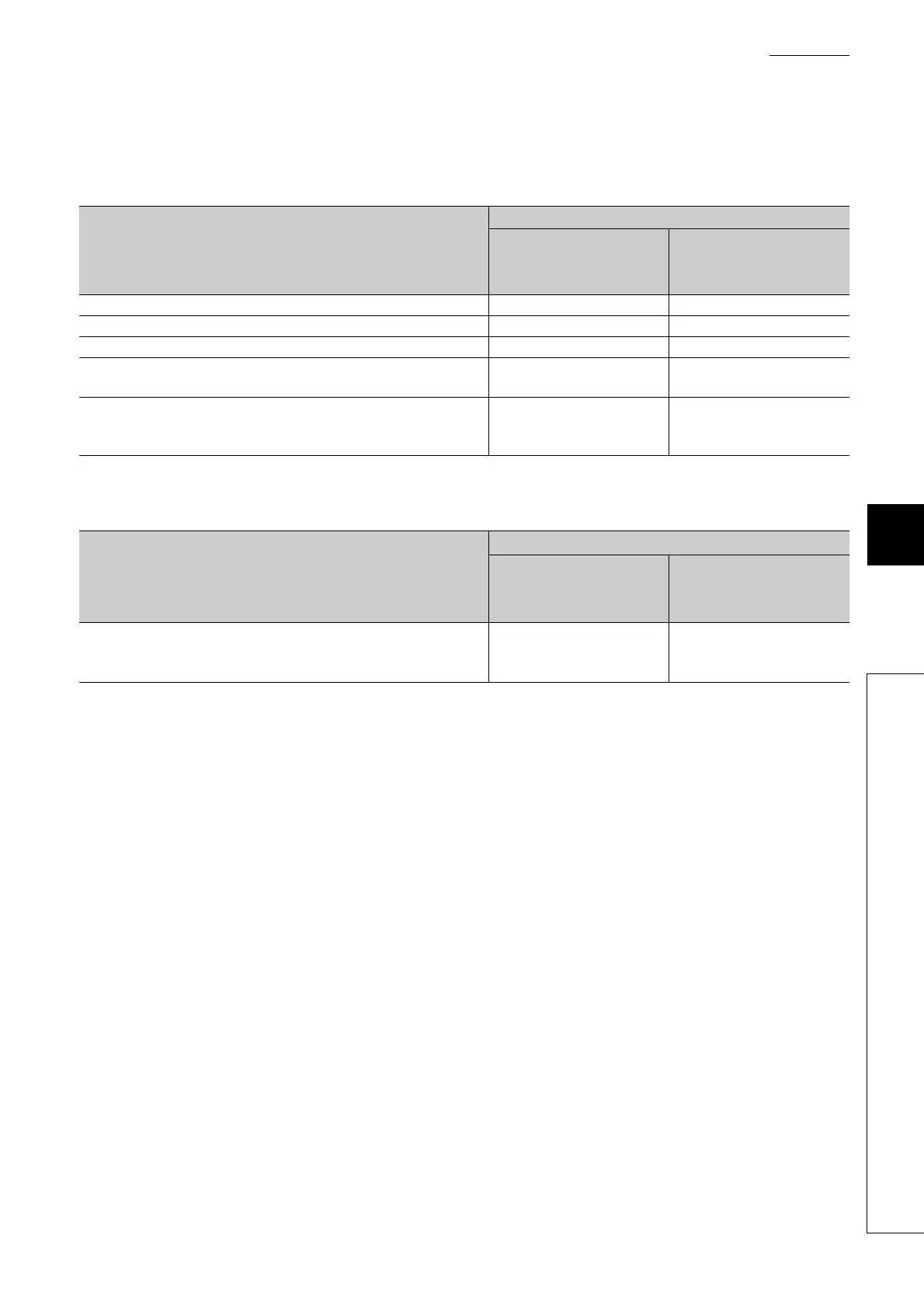

(b) Error clear

The following processing time is required to clear continuation errors stored in SD50 on the rising edge of

SM50 (Error reset).

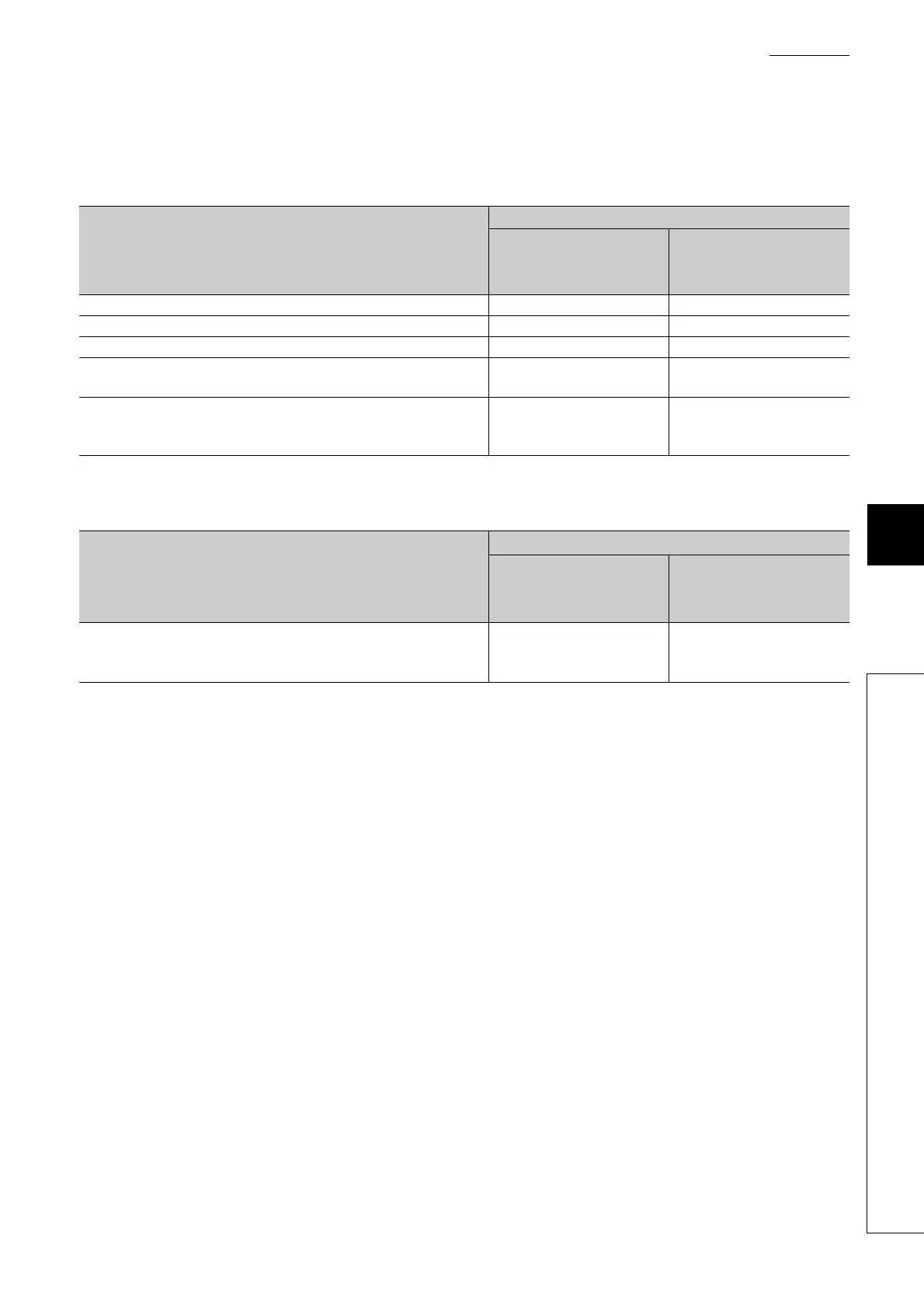

(c) Error clear by types

The following processing time is required to clear continuation errors by types.

(6) Device data latch processing time

When the latch range is set in the Device tab of the PLC parameter dialog box

*1 *2 *3

, the processing time listed in

the following tables is required. Each N1, N2, and N3 in the table indicates the following.

• N1: Number of devices specified to be latched (Count the latch range (1) and the latch range (2) as different

devices.)

• N2: Number of bit device points specified to be latched

• N3: Number of word device points specified to be latched

CPU module

Processing time in END processing

When the error is cleared

(the one detected by the

annunciator)

When the error is cleared

Q00UJCPU, Q00UCPU, Q01UCPU 0.185ms 0.180ms

Q02UCPU 0.180ms 0.175ms

Q03UD(E)CPU 0.068ms 0.062ms

Q04UD(E)HCPU, Q06UD(E)HCPU, Q10UD(E)HCPU, Q13UD(E)HCPU,

Q20UD(E)HCPU, Q26UD(E)HCPU, Q50UDEHCPU, Q100UDEHCPU

0.065ms 0.062ms

Q03UDVCPU, Q04UDVCPU, Q04UDPVCPU, Q06UDVCPU,

Q06UDPVCPU, Q13UDVCPU, Q13UDPVCPU,Q26UDVCPU,

Q26UDPVCPU

0.03ms 0.026ms

CPU module

Processing time in END processing

When the error is cleared

(the one detected by the

annunciator)

When the error is cleared

Q03UDVCPU, Q04UDVCPU, Q04UDPVCPU, Q06UDVCPU,

Q06UDPVCPU, Q13UDVCPU, Q13UDPVCPU, Q26UDVCPU,

Q26UDPVCPU

0.04ms 0.036ms

Loading...

Loading...