673

S.TO, SP.TO

9

2

3

4

4

6

7

8

9.1 Writing to the CPU Shared Memory of Host CPU

9.1.1 S.TO, SP.TO

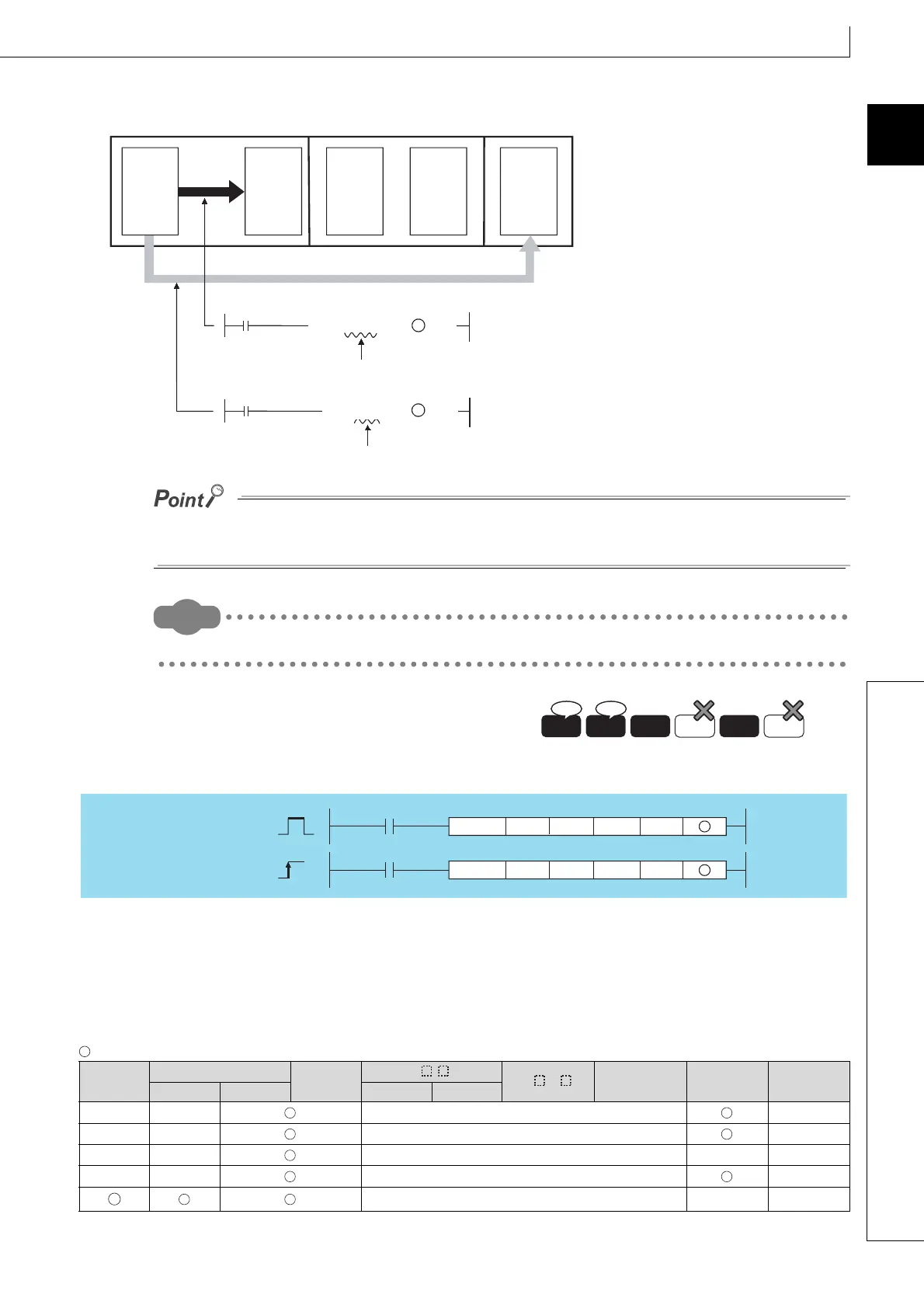

The following figure shows the processing performed when the TO instruction is executed in CPU No. 1.

Both of the S.TO and TO instructions can be used for the Basic model QCPU and Universal model QCPU to write data to

the CPU shared memory. However, use of the TO instruction is recommended to write data to the CPU shared memory of

the host CPU module, since use of S.TO instruction reduces the number of steps and processing time.

Remark

Refer to Page 428, Section 7.8.2 when writing to the buffer memory of the intelligent function module by the TO instruction.

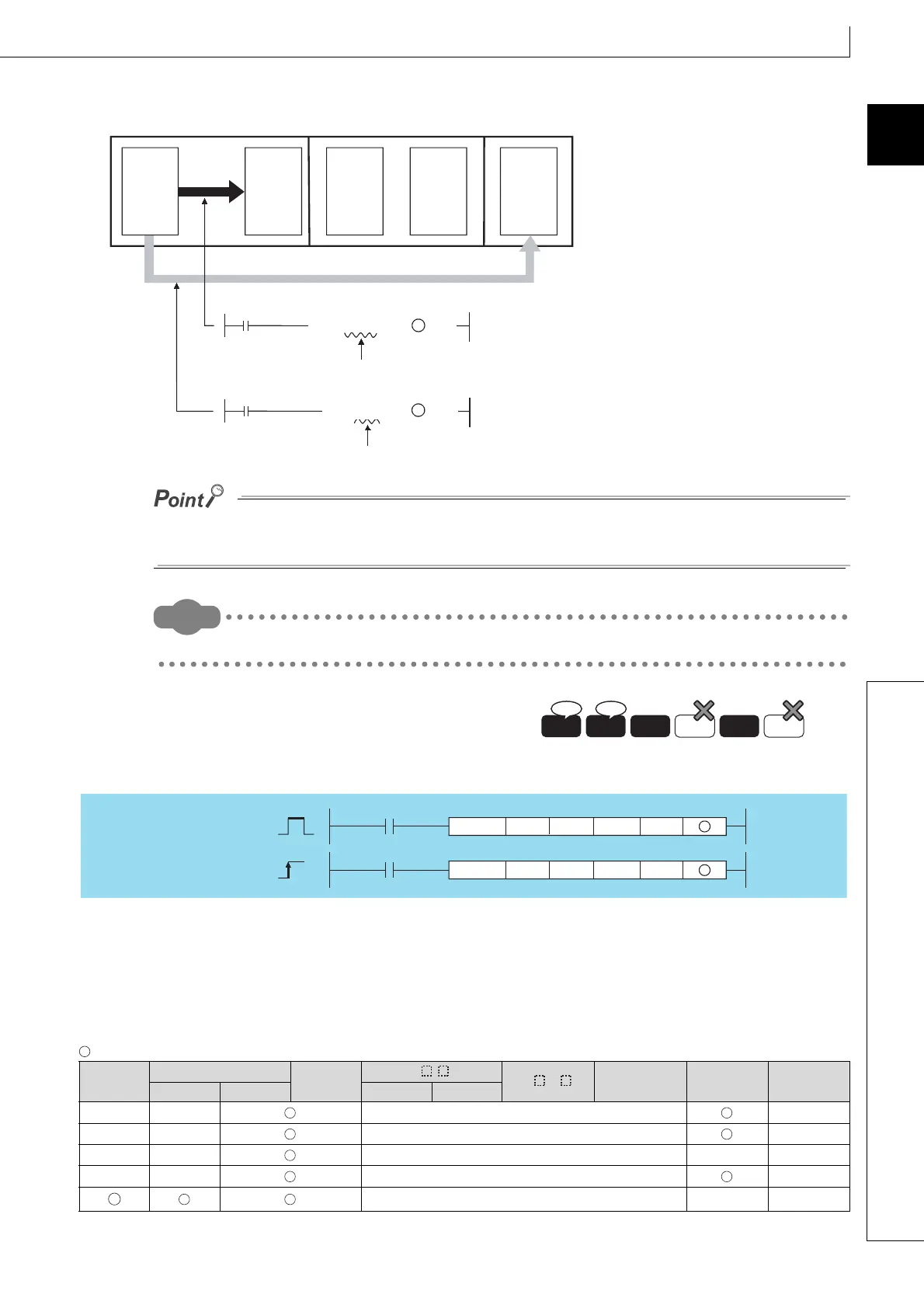

n1 : Head I/O number of the host CPU (BIN 16 bits)

n2 : CPU shared memory address of the write destination host CPU (BIN 16 bits)

•Basic model QCPU: 0 to 511

•High Performance model QCPU, Process CPU, Universal model QCPU: 0 to 4095

n3 : Head number of the devices where data to be written is stored (BIN 16 bits)

n4 : Number of data blocks to be written (BIN 16 bits)

•Basic model QCPU: 1 to 320

•High Performance model QCPU, Process CPU: 1 to 256

•Universal model QCPU: 1 to 2048

: Device of the host CPU which is turned ON for one scan by the completion of writing (bits)

9.1.1 S.TO, SP.TO Writing to host CPU shared memory

9.1.1

S.TO, SP.TO

• Q00CPU, Q01CPU: The serial number (first five digits) is

"04122" or later.

• High Performance model QCPU: Function version B or later

Setting

Data

Internal Devices

R, ZR

J\

U\G

Zn

Constants

K, H

Other

Bit Word Bit Word

n1 –– –– ––

n2 –– –– ––

n3 –– –– –– ––

n4 –– –– ––

–– –– ––

Designation of CPU shared memory in CPU No. 1

[ TO H3E0 n2 n3 ]

Designation of intelligent function module

[ TO H0 n2 n3 ]

Writes data

S

S

Device

memory

CPU

shared

memory

Device

memory

Buffer

memory

CPU

shared

memory

CPU No. 1

CPU No. 2

Intelligent

function module

Data

write

Redundant

LCPU

Basic

Process

High

performance

Universal

Ver. Ver.

Command

Command

n4

n4

n1

n1

n2

n2

S.TO

SP.TO

S.TO

SP.TO

n3

n3

D

D

D

D

Loading...

Loading...