689

1

10

3

4

6

6

7

8

10.1 Overview

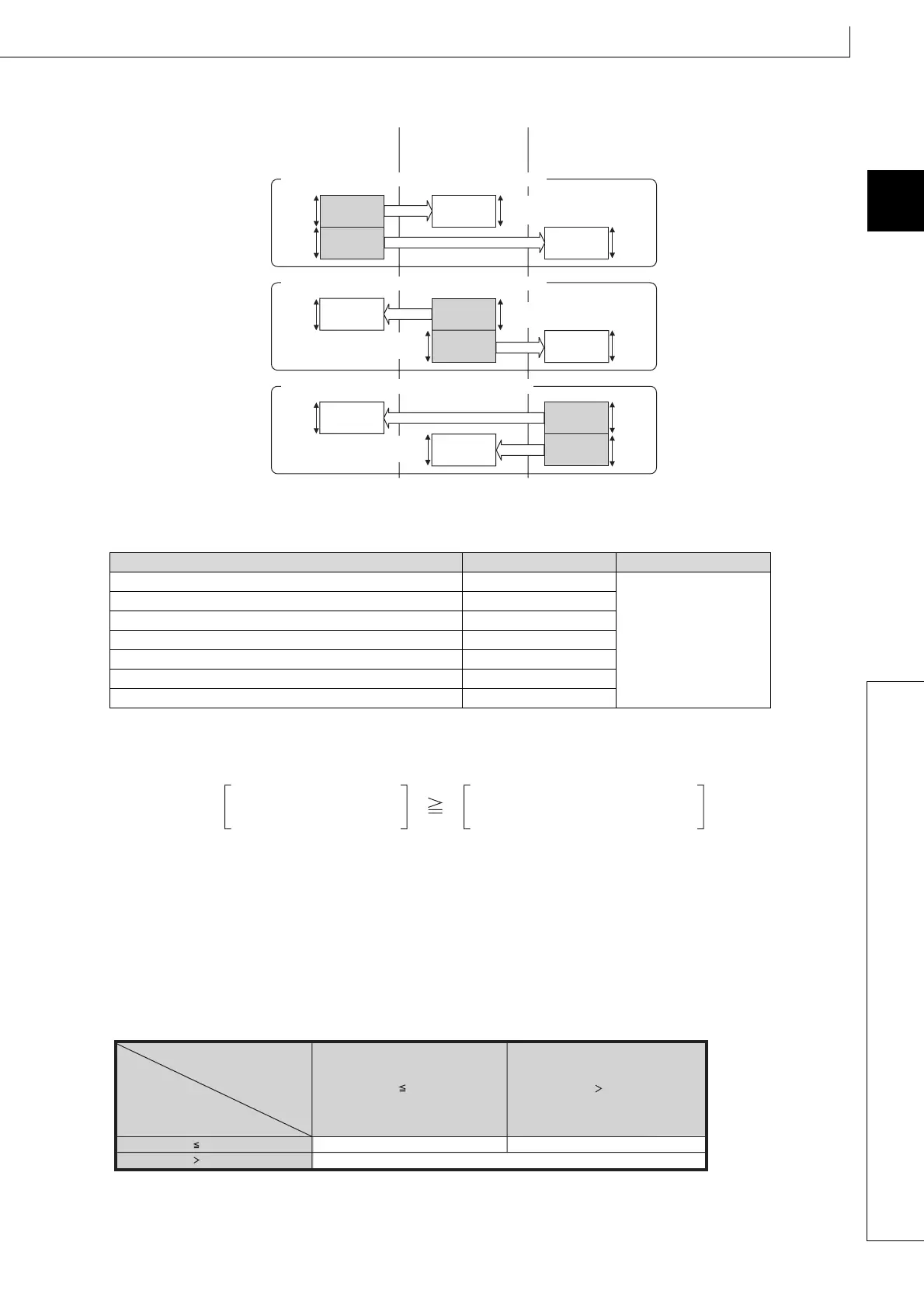

(b) The following shows configuration of the multiple CPU high speed transmission area when the multiple CPU system

is configured with three CPU modules and the system area size is 1k word.

(5) The number of blocks used for the instruction

The number of blocks used for the instruction depends on the number of write points.

The following table shows the number of blocks used for the instruction.

(6) The multiple CPU high-speed transmission dedicated instructions that can be executed concurrently

For the Universal model QCPU, the multiple CPU high-speed transmission dedicated instructions can be concurrently

executed within the range satisfying the following formula.

When the number of blocks used for the multiple CPU high-speed transmission dedicated instructions exceeds the total

number of blocks in the multiple CPU high speed transmission area, the instruction will not be executed in the scan (no

processing) but executed at the next scan.

Note that the instruction will be completed abnormally when the number of empty blocks in the multiple CPU high speed

transmission area is less than the setting values of SD796 to SD799 (maximum number of used blocks for multiple CPU

high-speed transmission dedicated instruction setting) at the execution of the instruction.

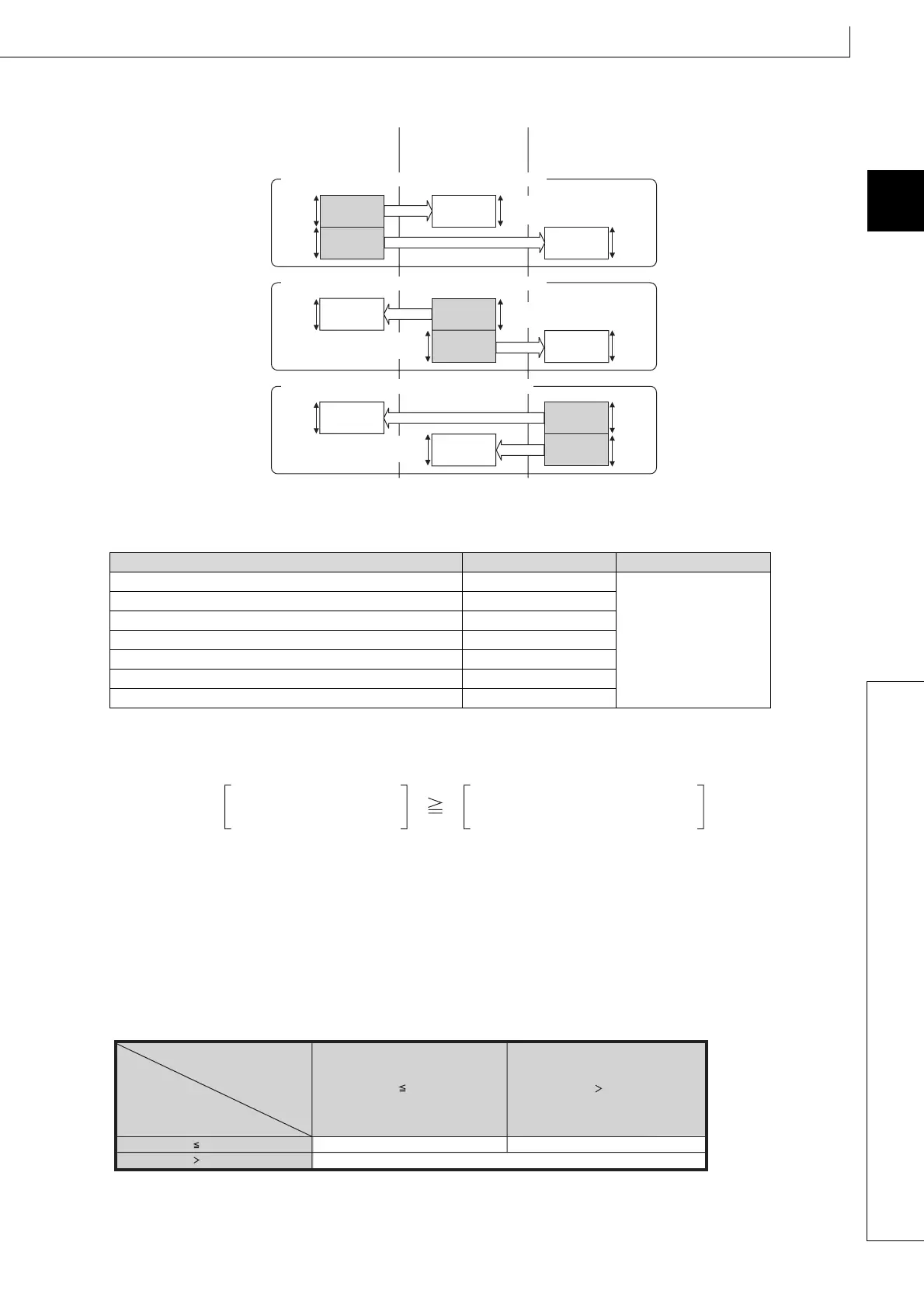

The following table shows execution possibility of the multiple CPU high-speed transmission dedicated instructions when

the number of empty blocks in the multiple CPU high speed transmission area is less than the number of blocks used for

the multiple CPU high-speed transmission dedicated instructions or the setting values of SD796 to SD799.

Number of write/read points specified by the instruction D(P).DDWR instruction D(P).DDRD instruction

1 to 4 1

1

5 to 20 2

21 to 36 3

37 to 52 4

53 to 68 5

69 to 84 6

85 to 100 7

Multiple CPU high speed

transmission area in

CPU No.1

Multiple CPU high speed

transmission area in

CPU No.2

Multiple CPU high speed

transmission area in

CPU No.3

Area to be sent from CP

U No.1 to CP

U No.s

2 and 3

22

blocks

22

blocks

22

blocks

22

blocks

Send area to

CPU No.2

Send area to

CPU No.3

Receive area from

CPU No.1

Receive area from

CPU No.1

Area to be sent from CP

U No.2 to CPU No.s 1 and 3

Area to sent from CP

U No.

3 to CP

U No.s 1 and 2

22

blocks

Receive area to

CPU No.2

Send area to

CPU No.1

Send area to

CPU No.3

22

blocks

22

blocks

Receive area to

CPU No.2

22

blocks

22

blocks

Receive area to

CPU No.3

22

blocks

Receive area to

CPU No.3

Send area to

CPU No.1

Send area to

CPU No.2

22

blocks

22

blocks

The number of blocks that

can be used in each CPU

Total number of blocks used for the

instructions concurrently executed

Magnitude relation between the number of blocks

used for the instructions*1 and

the number of empty

blocks

Magnitude relation

between SD setting value

and the number of empty blocks

SD setting value*

3

Number of empty blocks*

2

SD setting value*

3

Number of empty blocks*

2

Number of blocks used

for the instruction*1

Number of empty blocks*2

Number of blocks used

for the instruction*1

Number of empty blocks*2

Executed Not executed (no processing)

Completed abnormally

*1:The number of blocks used for the multiple CPU high-speed transmission dedicated instruction.

*2:The number of empty blocks in the multiple CPU high-speed transmission area.

*3:Setting values from SD796 of SD799.

Loading...

Loading...