96 SM-Applications Modules & Motion Processors User Guide

Issue Number: 4

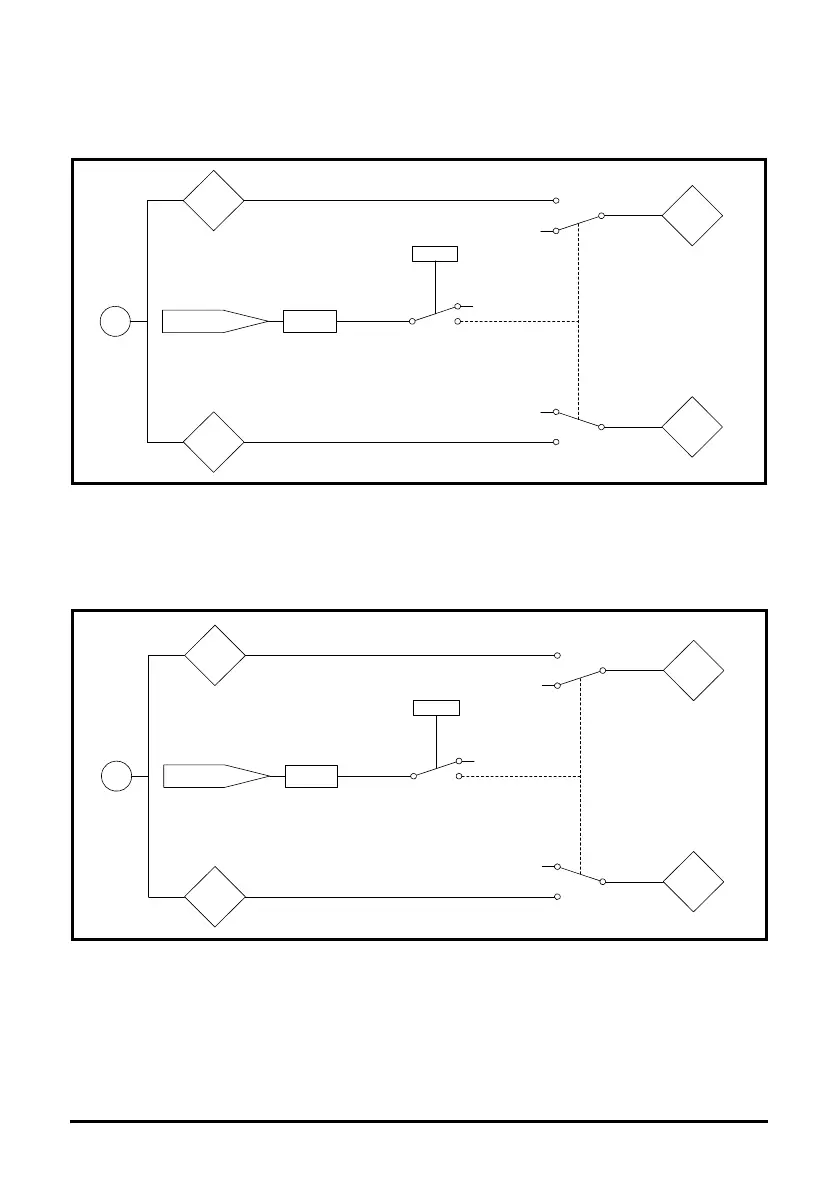

8.3 Marker pulse

The Second Processor is able to cache the position and revolution count at the point

when a Marker pulse is seen on the reference or feedback encoders.

Figure 8-5 Second Processor Reference Marker

The marker position is cached into Pr 90.35 and the marker revolution counter is cached

into Pr

90.36.

The user sets Pr

90.41 to a zero and the drive sets Pr 90.41 to a 1 EVERY time a

marker is detected. The marker data must be consumed before the next marker pulse.

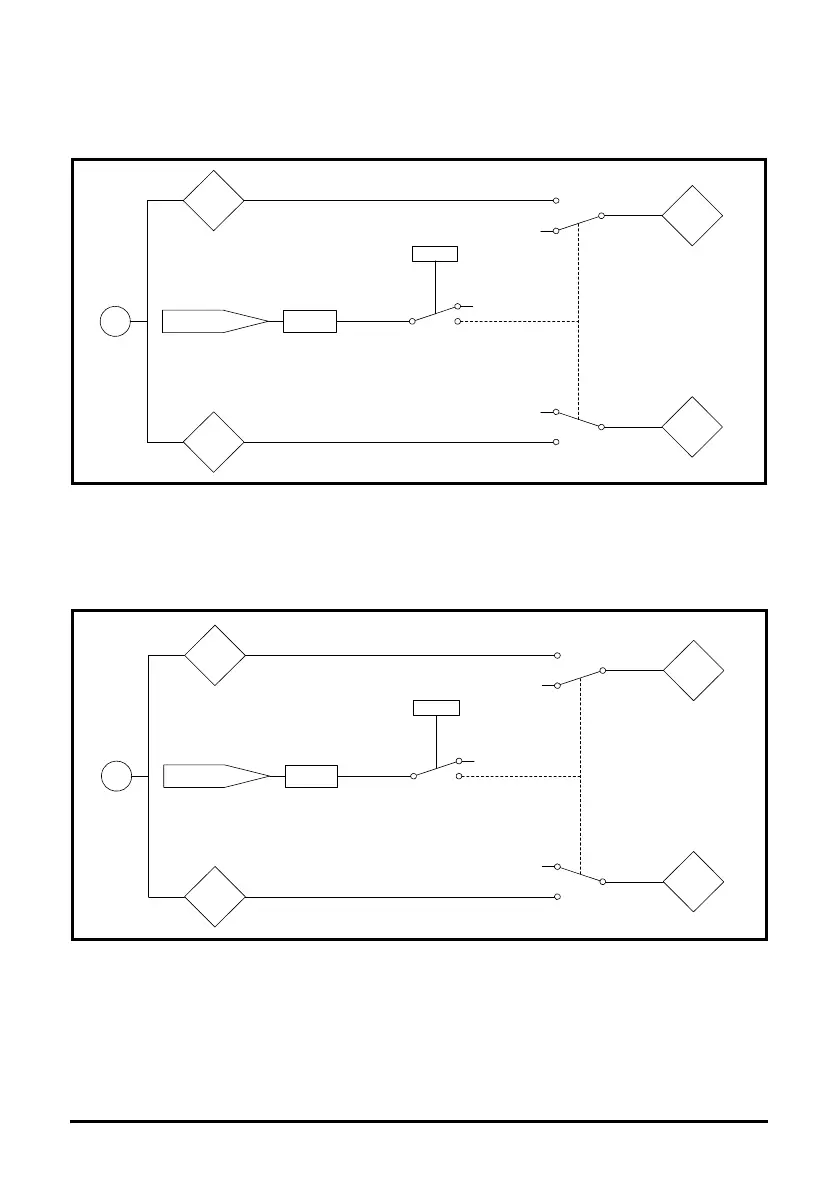

Figure 8-6 Second Processor Feedback Marker

The marker position is cached into Pr 90.25 and the marker revolution counter is cached

into Pr

90.26.

The user sets Pr

90.42 to a zero and the drive sets Pr 90.42 to a 1 EVERY time a

marker is detected. The marker data must be consumed before the next marker pulse.

0

Reference

encoder

Internal drive

encoder

position

counter

Marker pulse

#90.41

#90.45

#90.36

#90.35

0

1

0

1

1

Reference encoder

marker position

Internal drive

encoder

revolution

counter

Reference encoder

marker turns

E

0

Feedback

encoder

Internal drive

encoder

position

counter

Marker pulse

#90.42

#90.46

#90.26

#90.25

0

1

0

1

1

Feedback encoder

marker position

Internal drive

encoder

revolution

counter

Feedback encoder

marker turns

E

Loading...

Loading...