The pin assignment is structured as follows:

Terminal Assignment Terminal Assignment Explanations

1 U

V0

2 U

V1

Terminal 1 to 4:

U

Vn

: Sensor supply, channel n

Terminal 5 to 8:

I

n

+: Input signal, channel n

Terminal 9 to 12:

H

n

+: HART input signal, channel n

Terminal 13 to 16:

M

n

: Ground; channel n

1P1: Supply voltage L+ of the voltage

bus 1P

2P1: Supply voltage L+ of the voltage

bus 2P

1P2: Ground reference of the voltage

bus 1P

2P2: Ground reference of the voltage

bus 2P

1P1

L+

24VDC

M

1P2

2P1

L+

24VDC

M

2P2

MAX. 10 A

7

I2+

1

UV0

3

UV2

5

I0+

UV3

UV1

I3+

I1+

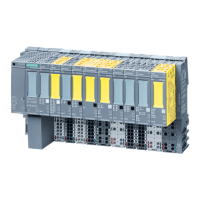

AI 2-/4-wire

15 16

9

10

11

12

13 14

M2

H0+

H2+

M0

H3+

H1+

M1

M3

8

2

4

6

3 U

V2

4 U

V3

5 I

0

+ 6 I

1

+

7 I

2

+ 8 I

3

+

9 H

0

+ 10 H

1

+

11 H

2

+ 12 H

3

+

13 M

0

14 M

1

15 M

2

16 M

3

1P1 L+ 1P2 M

2P1

1

L+ 2P2 M

1

If the module is inserted in a TB45R-P16 terminal block suitable for IO redundancy, the voltage at this terminal is 1P3.

Connection

4.1 Terminal assignment

AI 4xI 2-/4-wire HART ISOL HA

16 Equipment Manual, 07/2022, A5E50101523-AB

Loading...

Loading...