PM0214 Rev 10 215/262

PM0214 Core peripherals

261

4.3.7 Interrupt priority register x (NVIC_IPRx)

Address offset: 0x400 + 0x04 * x, (x = 0 to 59)

Reset value: 0x0000 0000

Required privilege: Privileged

The NVIC_IPRx (x = 0 to 59) byte-accessible registers provide 8-bit priority fields IP[N]

(N = 0 to 239) for each of the 240 interrupts. Every register holds four IP[N] fields of the

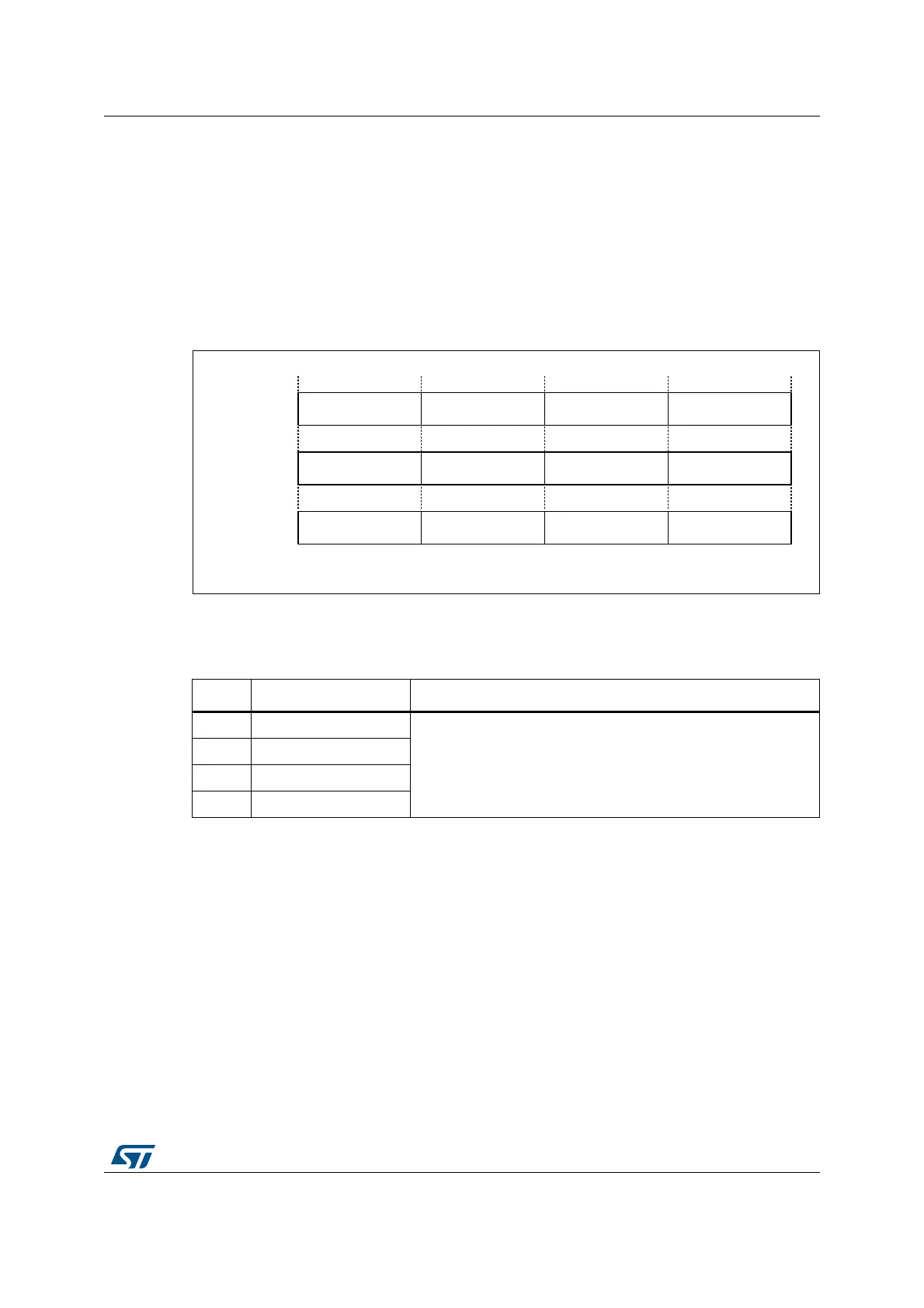

CMSIS interrupt priority array, as shown in Figure 19.

Figure 19. Mapping of IP[N] fields in NVIC_IPRx registers

The following table shows the bit assignment of any NVIC_IPRx register. Each IP[N] field

order can be expressed as N = 4 * x + byte offset.

See Interrupt set-enable register x (NVIC_ISERx) on page 210 for a view of the interrupt

priorities from the software perspective.

Note: The number of interrupts is product-dependent. Refer to reference manual/datasheet of

relevant STM32 product for related information.

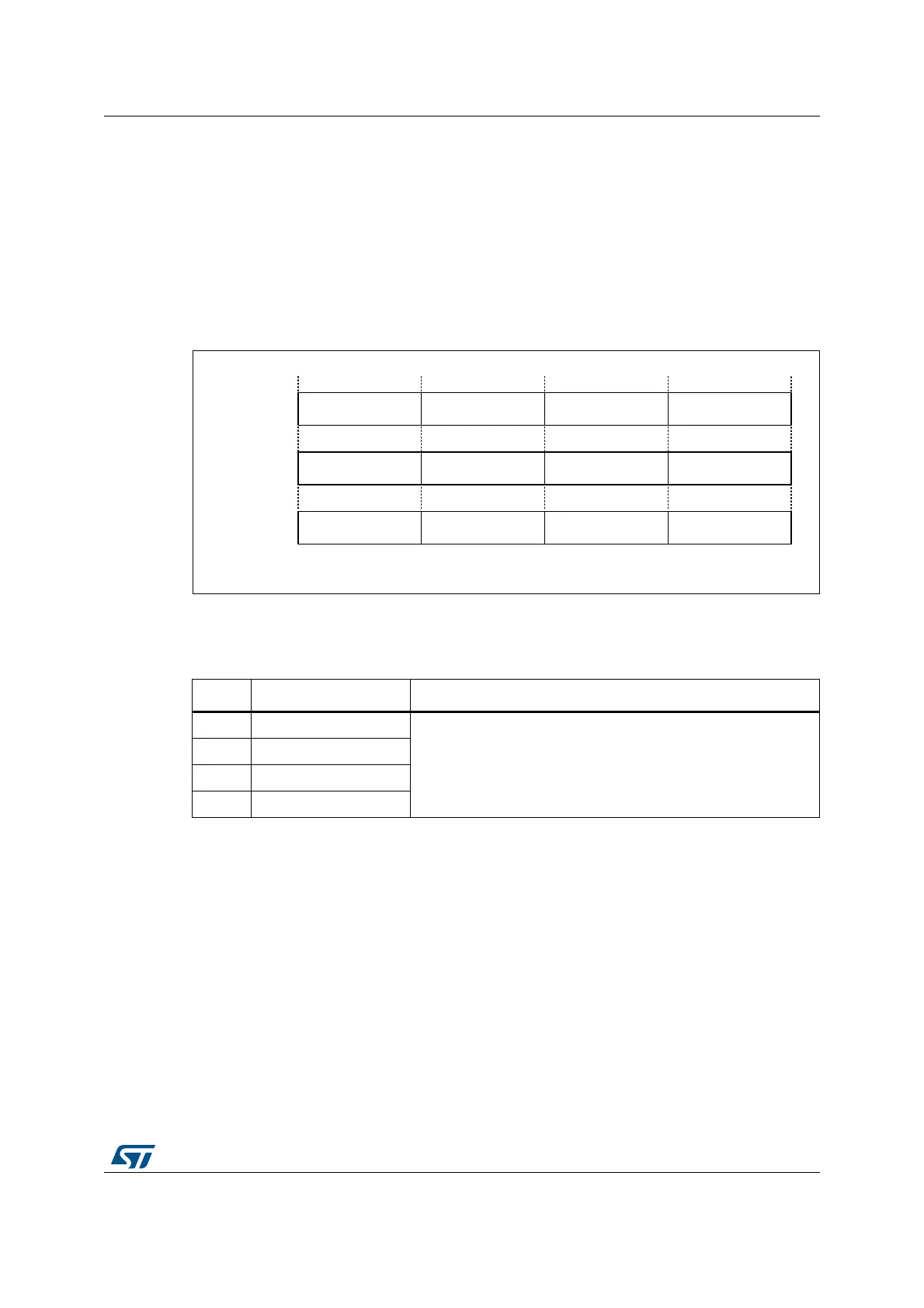

Table 47. NVIC_IPRx bit assignment

Bits Name Function

[31:24] Priority, byte offset = 3

Each priority field holds a priority value, 0-255. The lower the

value, the greater the priority of the corresponding interrupt. The

processor implements only bits[7:4] of each field, bits[3:0] read

as zero and ignore writes.

[23:16] Priority, byte offset = 2

[15:8] Priority, byte offset = 1

[7:0] Priority, byte offset = 0

MSv47990V1

IP[3] IP[2] IP[1] IP[0]

IP[4x+3] IP[4x+2] IP[4x+1] IP[4x]

NVIC_IPR0

NVIC_IPRx

IP[239] IP[238] IP[237] IP[236]

NVIC_IPR59

0781516232431

Loading...

Loading...