PM0214 Rev 10 67/262

PM0214 The STM32 Cortex-M4 instruction set

261

Condition code suffixes

The instructions that can be conditional have an optional condition code, shown in syntax

descriptions as

{cond}

. Conditional execution requires a preceding

IT

instruction. An

instruction with a condition code is only executed if the condition code flags in the APSR

meet the specified condition. Table 24 shows the condition codes to use.

You can use conditional execution with the

IT

instruction to reduce the number of branch

instructions in code.

Table 24 also shows the relationship between condition code suffixes and the N, Z, C, and V

flags.

Specific example 1: Absolute value shows the use of a conditional instruction to find the

absolute value of a number. R0 = ABS(R1).

Specific example 1: Absolute value

MOVSR0, R1; R0 = R1, setting flags

IT MI ; IT instruction for the negative condition

RSBMIR0, R1, #0; If negative, R0 = -R1

Specific example 2: Compare and update value shows the use of conditional instructions to

update the value of R4 if the signed value R0 and R2 are greater than R1 and R3

respectively.

Specific example 2: Compare and update value

CMP R0, R1 ; compare R0 and R1, setting flags

ITT GT ; IT instruction for the two GT conditions

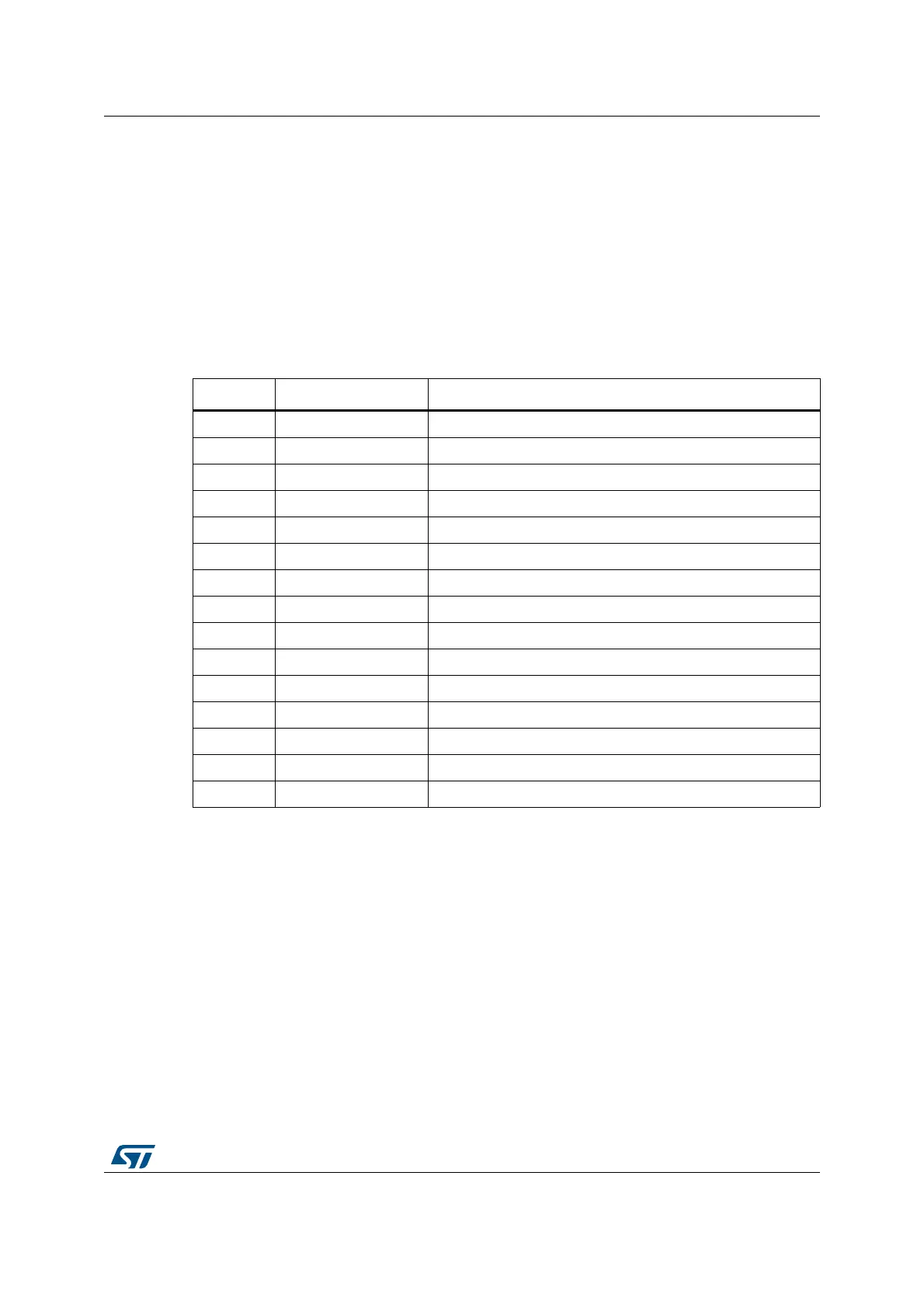

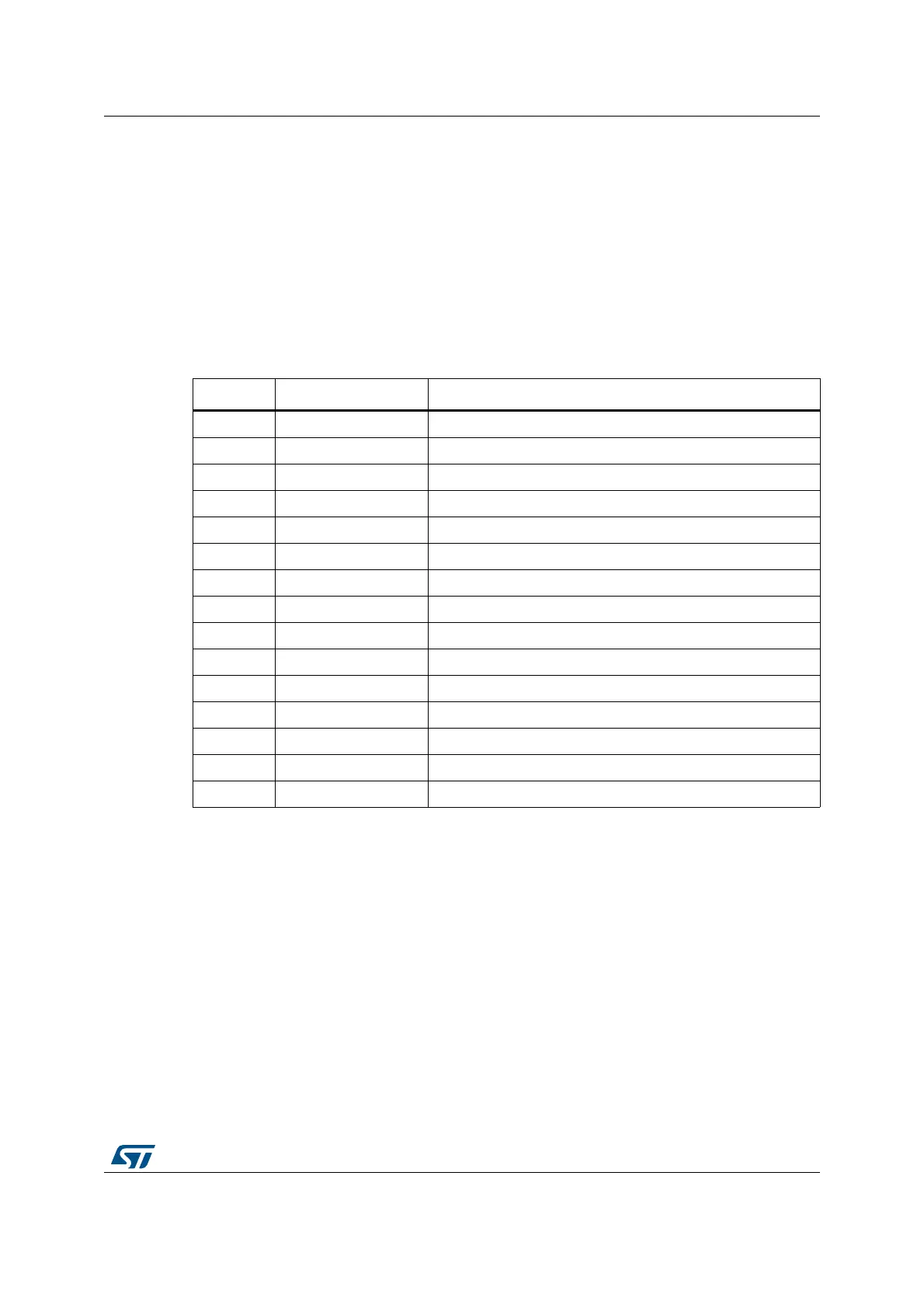

Table 24. Condition code suffixes

Suffix Flags Meaning

EQ Z = 1 Equal

NE Z = 0 Not equal

CS or HS C = 1 Higher or same, unsigned ≥

CC or LO C = 0 Lower, unsigned <

MI N = 1 Negative

PL N = 0 Positive or zero

VS V = 1 Overflow

VC V = 0 No overflow

HI C = 1 and Z = 0 Higher, unsigned >

LS C = 0 or Z = 1 Lower or same, unsigned

≤

GE N = V Greater than or equal, signed ≥

LT N != V Less than, signed <

GT Z = 0 and N = V Greater than, signed >

LE Z = 1 and N != V Less than or equal, signed

≤

AL Can have any value Always. This is the default when no suffix is specified.

Loading...

Loading...