PM0214 Rev 10 225/262

PM0214 Core peripherals

261

4.4.3 Interrupt control and state register (ICSR)

Address offset: 0x04

Reset value: 0x0000 0000

Required privilege: Privileged

The ICSR:

• Provides:

– A set-pending bit for the Non-Maskable Interrupt (NMI) exception

– Set-pending and clear-pending bits for the PendSV and SysTick exceptions

• Indicates:

– The exception number of the exception being processed

– Whether there are preempted active exceptions

– The exception number of the highest priority pending exception

– Whether any interrupts are pending.

Caution: When you write to the ICSR, the effect is unpredictable if you:

• Write 1 to the PENDSVSET bit and write 1 to the PENDSVCLR bit

• Write 1 to the PENDSTSET bit and write 1 to the PENDSTCLR bit.

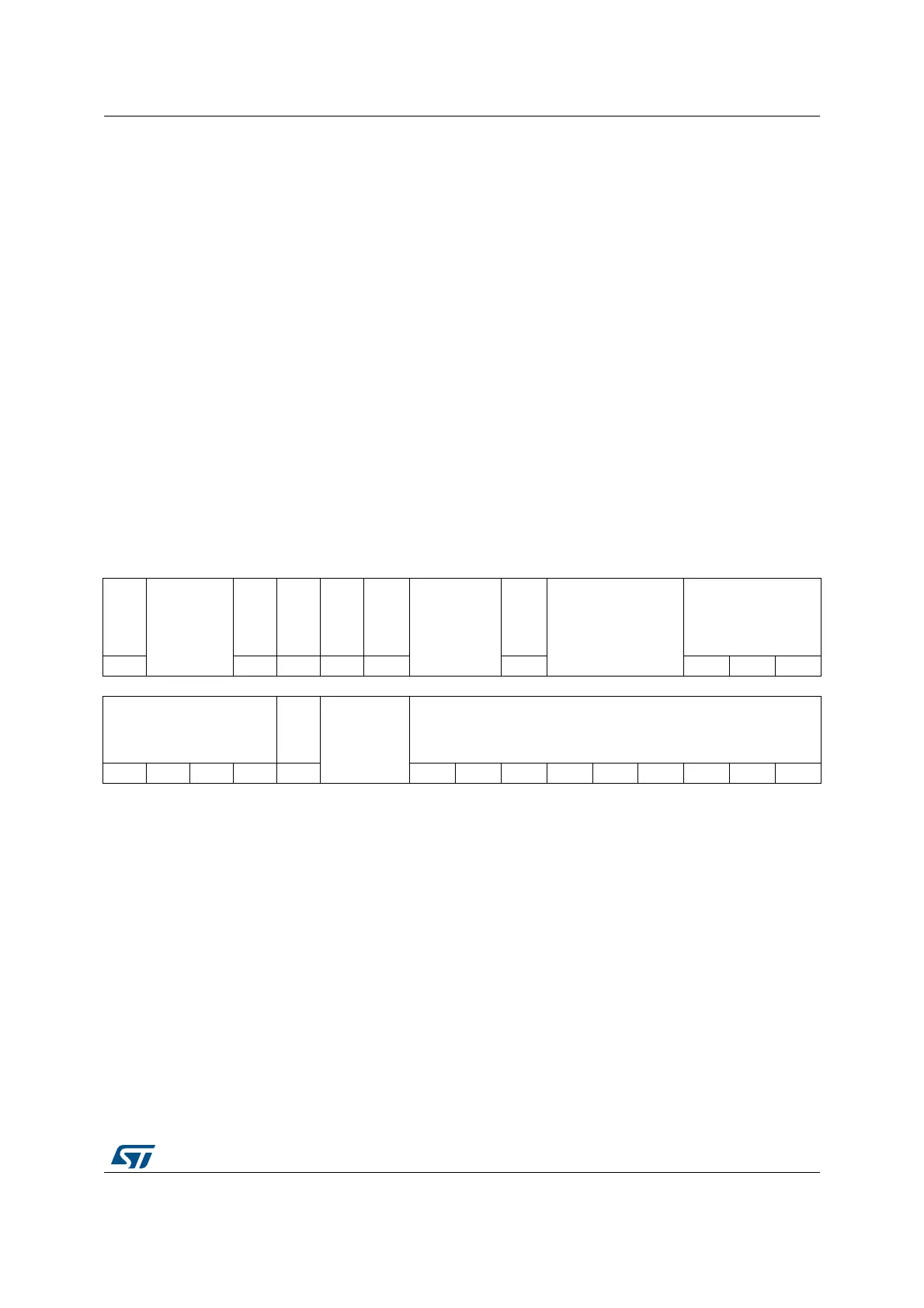

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

NMIPENDSET

Reserved

PENDSVSET

PENDSVCLR

PENDSTSET

PENDSTCLR

Reserved

ISRPENDING

Reserved

VECTPENDING[6:4]

rw rw w rw w r r r r

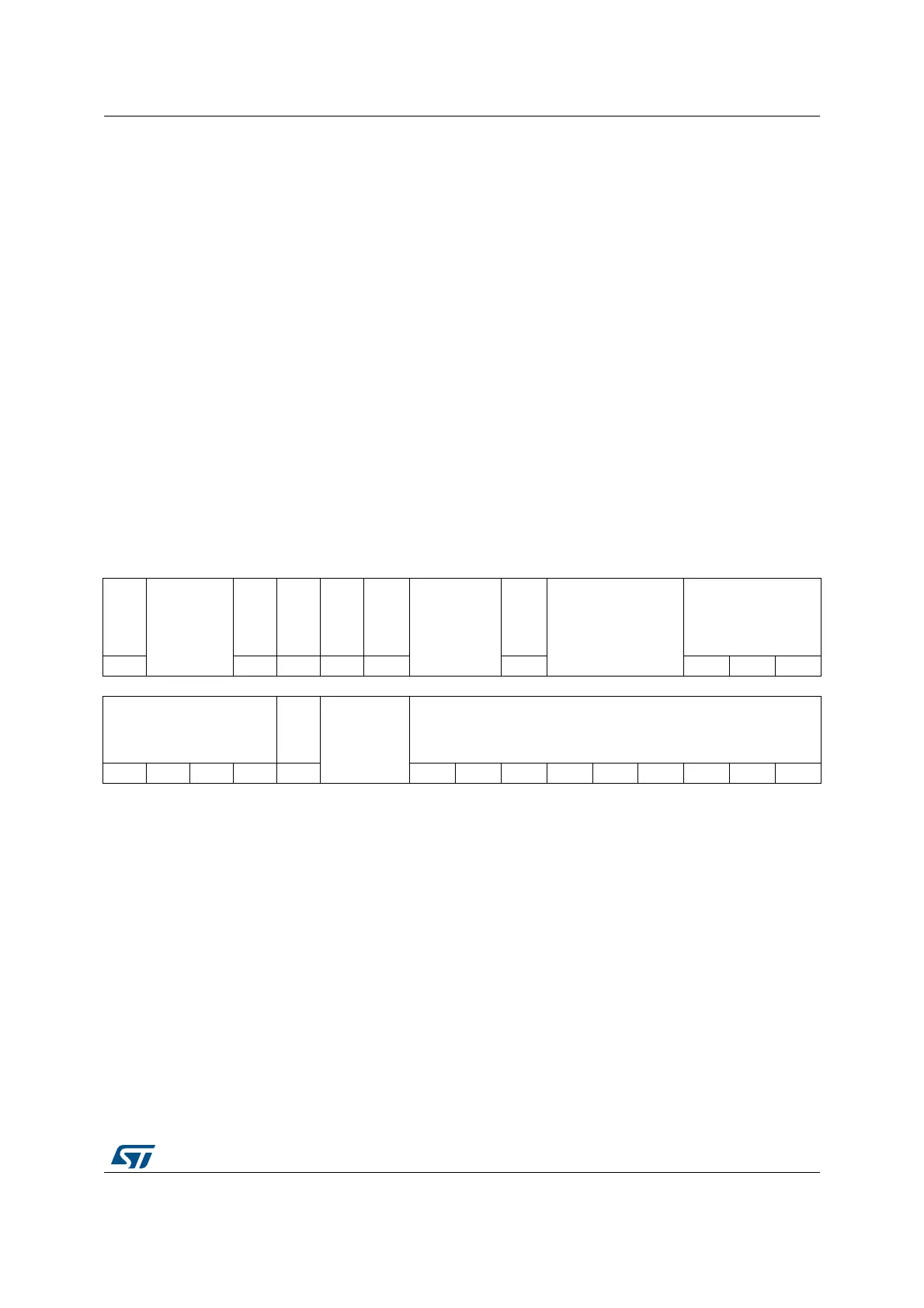

1514131211109876543210

VECTPENDING[3:0]

RETOBASE

Reserved

VECTACTIVE[8:0]

rrrrr rwrwrwrwrwrwrwrwrw

Bit 31 NMIPENDSET: NMI set-pending bit.

Write:

0: No effect

1: Change NMI exception state to pending.

Read:

0: NMI exception is not pending

1: NMI exception is pending

Because NMI is the highest-priority exception, normally the processor enter the NMI

exception handler as soon as it registers a write of 1 to this bit, and entering the handler clears

this bit to 0. A read of this bit by the NMI exception handler returns 1 only if the NMI signal is

reasserted while the processor is executing that handler.

Bits 30:29 Reserved

Loading...

Loading...