PM0214 Rev 10 205/262

PM0214 Core peripherals

261

SIZE field values

The SIZE field defines the size of the MPU memory region specified by the MPU_RNR

regsiter as follows:

(Region size in bytes) = 2

(SIZE+1)

The smallest permitted region size is 32B, corresponding to a SIZE value of 4. Table 43

gives example SIZE values, with the corresponding region size and value of N in the

MPU_RBAR.

Bits 15:8 SRD: Subregion disable bits.

For each bit in this field:

0: corresponding sub-region is enabled

1: corresponding sub-region is disabled

See Subregions on page 198 for more information.

Region sizes of 128 bytes and less do not support subregions. When writing the attributes for

such a region, write the SRD field as 0x00.

Bits 7:6 Reserved, forced by hardware to 0.

Bits 5:1 SIZE: Size of the MPU protection region.

The minimum permitted value is 3 (b00010), see SIZE field values for more information.

Bit 0 ENABLE: Region enable bit.

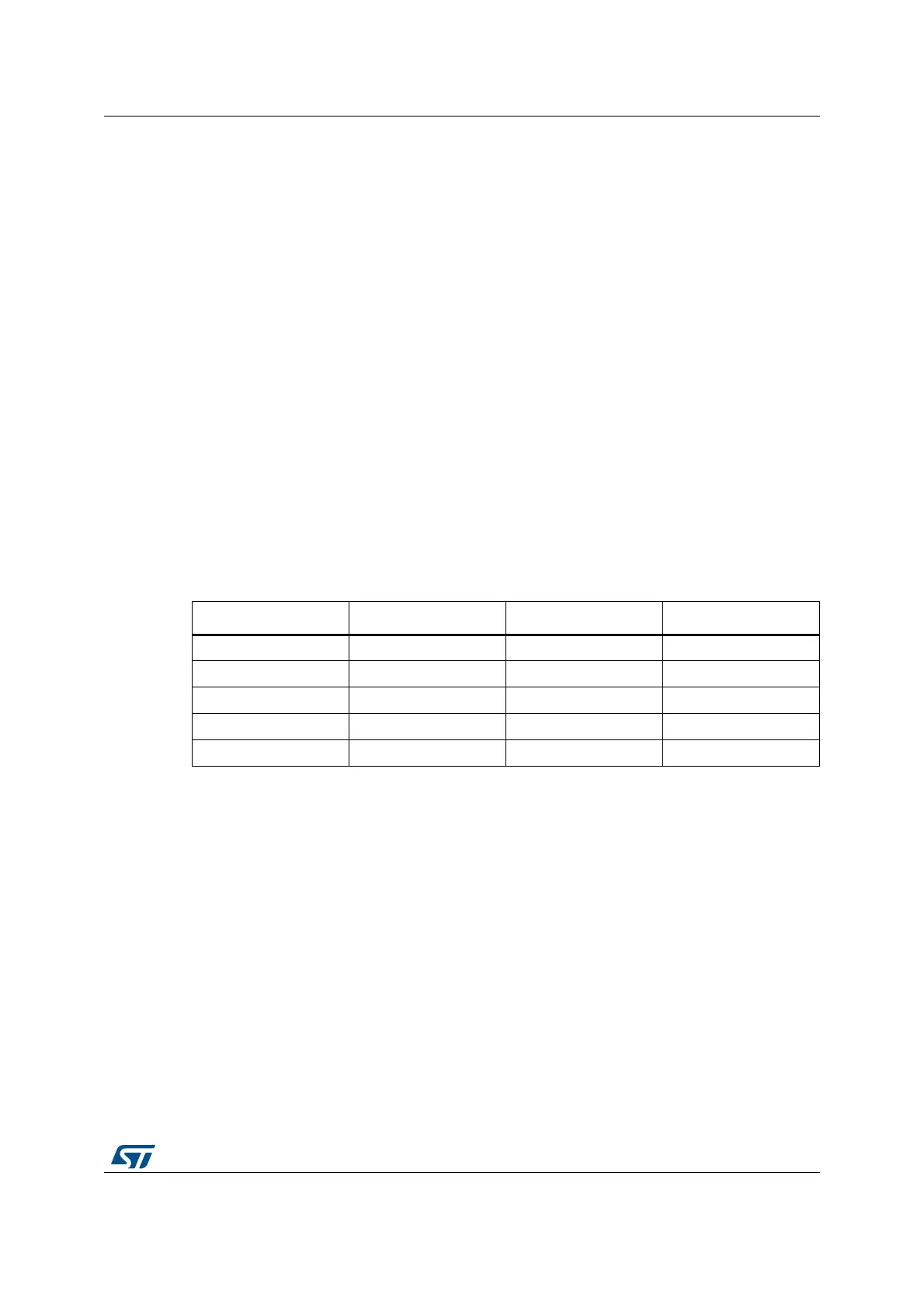

Table 43. Example SIZE field values

SIZE value Region size Value of N

(1)

1. In the MPU_RBAR register see Section 4.2.8 on page 203

Note

b00100 (4) 32B 5 Minimum permitted size

b01001 (9) 1KB 10 -

b10011 (19) 1MB 20 -

b11101 (29) 1GB 30 -

b11111 (31) 4GB b01100 Maximum possible size

Loading...

Loading...